# Performance Monitoring and Event-based Sampling for RISC-V

# **Tiago Alfredo Lopes Rocha**

Thesis to obtain the Master of Science Degree in

# **Electrical and Computer Engineering**

Supervisor: Prof. Dr. Pedro Filipe Zeferino Aidos Tomás Dr. Nuno Filipe Simões Santos Moraes da Silva Neves

# **Examination Committee**

Chairperson: Prof. Dr. António Manuel Raminhos Cordeiro Grilo Supervisor: Prof. Dr. Pedro Filipe Zeferino Aidos Tomás Member of the Committee: Prof. Dr. Aleksandar Ilic

December 2023

## Acknowledgements

At this moment, the end of my academic journey draws near. It was a fun and challenging part of my life I'm happy to have shared with so many wonderful people. Many of which were indispensable for me to complete this chapter and to whom I must thank.

First I would like to thank some of the Professors who crossed my path. Starting, of course with my thesis advisors, Prof. Pedro Tomás and Dr. Nuno Neves, as well as Prof. Nuno Roma. Without them and their ideas, suggestions and corrections this work would have not been possible. One more Professor from IST I owe a special thanks is Prof. João Paulo Ferreira da Silva, who truly made me believe that with hard work and dedication, I could complete this degree. Also, to my high school Professor who unfortunately is not among us anymore, José Luís Moraes, in whose classes I learned that Engineering was the right path for me.

Then, to my partner Patícia, who has always been by my side and supported me through the highs and lows of not only this work but also of my life, never letting me forget who I am and giving me unconditional support.

To my parents, Cristina and Rui, for raising me into the person I am today and always being proud of what I achieve. Also to my sister, Telma, who was my first teacher, showing me how to write and count; the true beginning of my academic education.

I would also like to thank Diogo and Vitor, for sharing these years with me, helping me in times of trouble and celebrating with me in times of victory.

Finally, but not less importantly, I thank everyone I met along the way, every friend I made and every Professor I was taught by. I'm certain they all helped me reach this point.

This work was partially supported by national funds through Fundação para a Ciência e a Tecnologia (FCT) under projects UIDB/50021/2020, 2022.06780.PTDC, and from the European High Performance Computing Joint Undertaking (JU) under Framework Partnership Agreement No 800928 and Specific Grant Agreement No 101036168 (EPI SGA2). The JU receives support from the European Union's Horizon 2020 research and innovation programme and from Croatia, France, Germany, Greece, Italy, Netherlands, Portugal, Spain, Sweden, and Switzerland.

# Declaration

I declare that this document is an original work of my own authorship and that it fulfills all the requirements of the Code of Conduct and Good Practices of the Universidade de Lisboa.

## Abstract

Increased attention to RISC-V open Instruction Set Architecture (ISA), has fueled its move from embedded devices to the high-performance computing arena, with the proliferation of RISC-V-based accelerators. However, the absence of powerful performance monitoring tools often results in poorly optimized applications and, consequently, limited computing performance. While the RISC-V ISA already defines a Hardware Performace Monitor and offers support for the Linux *perf\_events* subsystem, research and development on RISC-V-based devices have been more focused on architectures and compilers rather than tools to support monitoring performance. To overcome this limitation, the introduction of *PAPI* library support for RISC-V processors is proposed in this thesis, and a Precise Event Sampling system specification compatible with future *PAPI* integration is presented along with a minimal implementation proof-of-concept. The conducted testing and evaluation of the *PAPI* port were carried out on a SiFive Unmatched board, but the proposed changes, and the corresponding implementation, are easily portable to other systems. The proof of concept for RISC-V Precise Event Sampling was implemented on a CVA6 processor.

It was found that, when compared to directly using *perf\_events*, *PAPI* presents a large overhead;  $83360\mu s$  in comparison with *perf\_events*  $100.24\mu s$ . Nevertheless, most of it  $(81200\mu s)$  is concentrated in the initialization of the library, which only occurs once per program execution.

**Keywords:** RISC-V Processors, Performance Monitoring, Precise Event Sampling, PAPI

## Resumo

A crescente atenção dada à arquitetura de código aberto RISC-V impulsionou a sua transição de dispositivos embedded para a arena de computação de alto desempenho, com a proliferação de aceleradores baseados em RISC-V. No entanto, a ausência de ferramentas de monitorização de desempenho frequentemente resulta em aplicações pouco otimizadas e, consequentemente, num desempenho de computação limitado. Embora a arquitetura RISC-V já defina um Monitor de Desempenho de Hardware e ofereça suporte para o subsistema *perf\_events* do Linux, a pesquisa e o desenvolvimento em dispositivos baseados em RISC-V têm-se concentrado mais em arquiteturas e compiladores do que em ferramentas de suporte à monitorização de desempenho. Para superar essa limitação, a introdução do suporte à biblioteca *PAPI* para processadores RISC-V é proposta neste documento, juntamente com uma futura integração no *PAPI*, juntamente com uma prova de conceito de implementação mínima. Os testes e a avaliação do *PAPI* foram realizados em uma placa SiFive Unmatched, mas as alterações propostas e a implementação correspondente são facilmente portáveis para outros sistemas. A prova de conceito para a Amostragem Precisa de Eventos coNA6.

Foi constatado que, em comparação com o uso direto do *perf\_events*, o *PAPI* apresenta um overhead significativo;  $83360\mu s$  em comparação com  $100.24\mu s$  do *perf\_events*. No entanto, a maior parte ( $81200\mu s$ ) está concentrada na inicialização da biblioteca, que ocorre apenas uma vez por execução do programa.

**Palavras-Chave:** Processadores RISC-V, Monitorização de Desempenho, Amostragem Precisa de Eventos, PAPI

# Contents

| С  | onten | its     |                                                    | xi   |

|----|-------|---------|----------------------------------------------------|------|

| Li | st of | Figure  | 3                                                  | xiv  |

| Li | st of | Tables  |                                                    | xv   |

| Li | sting | s       |                                                    | xvi  |

| Gl | lossa | ry      |                                                    | xvii |

| 1  | Intro | oductio | n                                                  | 1    |

|    | 1.1   | Object  | lives                                              | 3    |

|    | 1.2   |         | butions                                            |      |

|    | 1.3   | Docun   | nent Outline                                       | 4    |

| 2  | Bac   | kgroun  | id and State-Of-The-Art                            | 5    |

|    | 2.1   | RISC-   | V ISA                                              | 6    |

|    |       | 2.1.1   | Base Integer ISA and Extensions                    | 6    |

|    |       | 2.1.2   | Hardware Performance Monitor                       | 7    |

|    | 2.2   | SiFive  | U7 Core                                            | 8    |

|    |       | 2.2.1   | Fixed-Function Performance Monitoring Counters     | 8    |

|    |       | 2.2.2   | Event-Programmable Performance Monitoring Counters | 9    |

|    |       | 2.2.3   | Event Selector Encodings                           | 10   |

|    | 2.3   | CVA6    |                                                    | 12   |

|    |       | 2.3.1   | Performance Monitoring Unit                        | 12   |

|    |       | 2.3.2   | Platform-Level Interrupt Controller                | 13   |

|    | 2.4   | Moder   | n development on Hardware Performance Counters     | 14   |

|    |       | 2.4.1   | Hardware Multiplexing                              | 14   |

|    | 2.5   | Perf_e  | events                                             | 14   |

|    | 2.6   | Perfor  | mance API - PAPI                                   | 15   |

|    |       | 2.6.1   | Original Design                                    | 16   |

|    |       | 2.6.2   | libpfm4                                            | 19   |

|    |       | 2.6.3   | How PAPI Reads Event Count Values                  | 20   |

|   | 2.7  | Precis  | e Event Sampling                                                      | 20 |

|---|------|---------|-----------------------------------------------------------------------|----|

|   |      | 2.7.1   | Intel PEBS                                                            | 21 |

|   |      | 2.7.2   | Precise Event Sampling Support in PAPI                                | 21 |

|   | 2.8  | Summ    | nary                                                                  | 22 |

| 3 | Port | ting PA | PI to RISC-V                                                          | 24 |

|   | 3.1  | Gener   | al RISC-V Support                                                     | 25 |

|   |      | 3.1.1   | Thread Context For Counter Overflow                                   | 26 |

|   |      | 3.1.2   | Memory Barrier                                                        | 26 |

|   |      | 3.1.3   | Access To Cycle Counter                                               | 27 |

|   |      | 3.1.4   | Vendor Identification                                                 | 27 |

|   |      | 3.1.5   | RISC-V Event List Entry Type, Register Type and PMU Configurtion Type | 28 |

|   |      | 3.1.6   | Functions To Interact With The Event List                             | 30 |

|   |      | 3.1.7   | Get Event Encoding and <i>perf_events</i>                             | 31 |

|   |      | 3.1.8   | libpfm4 Makefile Changes                                              | 33 |

|   | 3.2  | SiFive  | U74-MC Support                                                        | 35 |

|   |      | 3.2.1   | Event List                                                            | 35 |

|   |      | 3.2.2   | PMU Model                                                             | 35 |

|   |      | 3.2.3   | PAPI Vendor Identification                                            | 37 |

|   |      | 3.2.4   | PAPI Presets                                                          | 39 |

|   |      | 3.2.5   | Case-Specific Note                                                    | 40 |

|   | 3.3  | Impler  | nentation Evaluation and Result Discussion                            | 40 |

|   | 3.4  | Summ    | ary                                                                   | 41 |

| 4 | Pred | cise Ev | ent Sampling on RISC-V                                                | 43 |

|   | 4.1  | Precis  | e Event Sampling Specification                                        | 44 |

|   |      | 4.1.1   | Objectives                                                            | 44 |

|   |      | 4.1.2   | Requirements                                                          | 44 |

|   |      | 4.1.3   | Specification                                                         | 45 |

|   | 4.2  | Precis  | e Event Sampling Architecture                                         | 46 |

|   |      | 4.2.1   | New CSRs                                                              | 46 |

|   |      | 4.2.2   | Memory-Mapped Location Address                                        | 47 |

|   |      | 4.2.3   | SBI-Like Interface Extension                                          | 47 |

|   |      | 4.2.4   | External Interrupt Request Control                                    | 47 |

|   |      | 4.2.5   | External Interrupt Handler                                            | 50 |

|   | 4.3  | Evalua  | ation and Result Discussion                                           | 51 |

|   | 4.4  | Summ    | nary                                                                  | 54 |

| 5  | Con   | clusion                | 56 |

|----|-------|------------------------|----|

|    | 5.1   | Contributions Achieved | 57 |

|    | 5.2   | Future Work            | 57 |

| Bi | bliog | raphy                  | 59 |

# **List of Figures**

| 2.1        | Counter-enable register mcounteren, [27]                               | 8  |

|------------|------------------------------------------------------------------------|----|

| 2.2        | Counter-inhibit register mcountinhibit, [27]                           | 8  |

| 2.3        | U74-MC Series Block Diagram [23]                                       | 9  |

| 2.4        | Event selector fields [23].                                            | 10 |

| 2.5        | Platform-Level Interrupt Controller (PLIC) communication flow, [10]    | 13 |

| 2.6        | PAPI architecture, modified from [1].                                  | 17 |

| 2.7        | Basic structure for hardware performance counting using PAPI           | 20 |

| 2.8        | One possible execution scenario of Intel PEBS. [21]                    | 22 |

| 4.1<br>4.2 | Overview of the system software structure                              | 45 |

|            | parts in blue were implemented, and parts in red were not implemented. | 46 |

| 4.3        | Register values during counting and interrupt request generation.      | 54 |

| 4.4        | Handler claim notification.                                            | 54 |

| 4.5        | Counter inhibition and sampling of the MEPC                            | 55 |

| 4.6        | Counter reset                                                          | 55 |

| 4.7        | Counting resumed and PLIC complete signal.                             | 55 |

# **List of Tables**

| 2.1 | mhpmeventX Register bit layout for overflow and filtering [23]                        | 10 |

|-----|---------------------------------------------------------------------------------------|----|

| 2.2 | mhpmevent Register on SiFive U7 [23]                                                  | 11 |

| 2.3 | mhpmevent Register on CVA6                                                            | 12 |

| 3.1 | Measured execution time overheads (average) of PAPI Library calls in relation to perf |    |

|     | events calls                                                                          | 40 |

| 3.2 | PAPI Library and perf_events event monitoring comparison with Gemm benchmark          | 40 |

| 4.1 | Reported resource utilization for the CVA6 processor.                                 | 51 |

# Listings

| 3.1  | Definitions in ucontext.h.                                      | 26 |

|------|-----------------------------------------------------------------|----|

| 3.2  | Changes to src/linux-context.h.                                 | 26 |

| 3.3  | Changes to src/mb.h.                                            | 27 |

| 3.4  | Changes to src/linux-timer.c.                                   | 27 |

| 3.5  | /proc/cpuinfo file on a RISC-V computer                         | 28 |

| 3.6  | Changes to src/linux-common.c for RISC-V identification.        | 28 |

| 3.7  | Definition of pfm_riscv_detect().                               | 29 |

| 3.8  | Definition of riscv_entry_t and pfm_riscv_reg_t                 | 29 |

| 3.9  | Definition of pfm_riscv_cfg                                     | 30 |

| 3.10 | Definition of pfm_riscv_get_event_first().                      | 30 |

| 3.11 | Definition of pfm_riscv_get_event_next()                        | 31 |

| 3.12 | Definition of pfm_riscv_event_is_valid()                        | 31 |

| 3.13 | Definition of pfm_riscv_validate_table()                        | 32 |

| 3.14 | Definition of pfm_riscv_get_event_info()                        | 32 |

| 3.15 | Definition of pfm_riscv_get_encoding().                         | 33 |

| 3.16 | Definition of pfm_riscv_get_perf_encoding().                    | 34 |

| 3.17 | Changes to src/libpfm4/config.mk.                               | 34 |

| 3.18 | Changes to src/libpfm4/lib/Makefile                             | 35 |

| 3.19 | Example of riscv_sifive_u74_pe[] event list.                    | 36 |

| 3.20 | Changes to libpfm4/include/perfmon/pfmlib.h.                    | 36 |

| 3.21 | Definition of pfm_riscv_detect_sifive_u74().                    | 36 |

| 3.22 | Definition of riscv_sifive_u74_support.                         | 38 |

| 3.23 | Changes to src/linux-common.c for RISC-V Vendor identification. | 38 |

| 3.24 | Changes to src/papi_events.csv                                  | 39 |

| 4.1  | Changes to core/perf_counters.sv.                               | 48 |

| 4.2  | Changes to machine/mtrap.c in riscv-pk library                  | 49 |

| 4.3  | HPM External Interrupt Request Control                          | 50 |

| 4.4  | Changes to corev_apu/tb/ariane_peripherals.sv                   | 50 |

| 4.5  | Changes to corev_apu/tb/ariane_peripherals.sv                   | 51 |

| 4.6  | PES test program.                                               | 53 |

# Glossary

- CSR Control Status Register

- EPI European Processor Initiative

- EU European Union

- HPC High Performance Computing

- HPM Hardware Performace Monitor

- ISA Instruction Set Architecture

- PMC Perfomance Monitoring Counter

- PMU Performance Monitoring Unit

- PLIC Platform-Level Interrupt Controller

- PES Precise Event Sampling

- SMP Symmetric Multiprocessing

- SoC System on Chip

- WARL Write Any Read Legal

# **CHAPTER 1**

# Introduction

In recent decades, microprocessors and computing technologies have found a way into almost all aspects of both our personal and collective lives. They have allowed humanity to develop in most areas of knowledge and given us the tools to enhance our standard of living to previously unimaginable heights. For example, areas like autonomous systems, medicine research and climate modeling have substantially benefited from the advancements in computing technology. In more recent times, the pursuit of High Performance Computing (HPC) in conjunction with data storage improvements allowed for a proliferation of cloud, data science and machine learning applications that together have created a platform in which even more scientific work can be developed.

For this trend to continue, all of the aforementioned technologies must be optimized to their greatest potential. The performance of computing technologies is evaluated not only purely in calculations per second, but also in how energetically efficient they are, being that the latter is recognized as the main challenge to achieve the milestone of exascale computing, or in other terms, executing 10<sup>18</sup> calculations per second. Even though this barrier has been crossed, there is much to be done in terms of efficiency.

The European Commission has acknowledged the strategic benefits of energetically efficient HPC by supporting the creation of the EuroHPC Joint Undertaking, an entity that has the objective of pooling European resources to buy, build and deploy supercomputers in the European Union (EU). EuroHPC is trying to achieve this by doing two things: firstly, creating a pan-European supercomputing infrastructure; and secondly, supporting the research and innovation of microprocessor and computing technologies inside the EU. The latter culminated in the formation of the European Processor Initiative (EPI), an initiative to develop a high-end, RISC-V-based microprocessor. The ISA represents the most widely adopted for open-source architecture projects and has gained substantial support not only from academia but also from emerging commercial vendors.

To achieve a goal such as exascale computing or even beyond that, programmers must be able to utilize as efficiently as possible all of the available hardware resources. This is a significant challenge, as it is generally hard to pinpoint the cause of a slowdown given the ever-increasing complexity of the microprocessor's architecture. In particular, this often requires the application of profiling techniques to correctly identify the bottleneck. On the other hand, during architecture codesign, this may be useful to optimize the architecture to the target application domains.

There are several ways to profile the performance of a system when running an application. One can use simple profiling techniques, like counting the time elapsed, but even if the programmer manages to identify the part of the source code that generates the unexpected slowdown, this technique does not explain why the slowdown occurred. If a well-tailored model of the processor exists, a simulator can be used to go over the execution and profile the usage of each component of the system, but this is often not the case, either due to commercial constraints or intellectual property limitations. Moreover, there are always modeling limitations that may impose a bias in the observation of performance bottlenecks.

Another way would be to utilize an Hardware Performace Monitor (HPM), usually packaged inside modern microprocessors. These devices can count a set of fixed and/or programmable events that occur inside the processor's pipeline (like instruction-cache misses or branches taken). With this information, a better image of the architecture components responsible for the performance bottlenecks can be observed.

This, in turn, allows tuning the application to account for the limitations found, or the design of the hardware to mitigate the observed problem.

Additionally, larger microprocessor manufacturers such as Intel or Arm offer catch-all tools that combine HPM event sampling with other techniques to aid the user with identifying which parts of their software need more attention. Again, open-source architectures based on the RISC-V ISA rarely, if ever, have this level of support from their manufacturers.

Although the RISC-V Foundation specifies that performance counters and a HPM must be packaged into a RISC-V core implementation [26], its open-source nature provides limited software support for accessing hardware performance counters. The official Linux kernel only supports the sampling of the cycles and instructions retired counters, leaving a lot of functionality out of bounds for anyone who desires to run Linux on their RISC-V processor.

This gap started to be bridged when support for the latest RISC-V HPM specification was introduced in the Linux Perf Kernel Driver [3], but there is yet no way to easily access the performance counters through a higher level interface library, like *PAPI*, and no further functionality is offered to the user besides manually specifying what events should be counted and reading them explicitly.

These are clear disadvantages when comparing RISC-V to any other already established architecture and may prevent the porting of user-level applications to the platform by setting a high barrier to entry for application developers who wish to utilize the available hardware to its full potential.

# 1.1 Objectives

It has become clear that, with today's computing technology, to achieve higher productivity and performance it is pivotal that great attention is given to process optimization, even if that means tailoring an application to a specific architecture to take advantage of its specificities or, if early enough in the architecture co-design phase, tailoring the architecture to the target application.

It is also evident that although support for the profiling tool *perf\_events* is available for RISC-V systems, no higher-level library is available to easily access the Hardware Performance Counters inside the application source code, as is usual to be done on other popular architectures.

Furthermore, the RISC-V specification for the HPM is still very simple when compared with the feature-rich implementations of architectures such as *x86* or *ARM*.

To help more efficient RISC-V software development and facilitate architecture codesign, this work is defined by two objectives. The first is to port an open-source and commonly used C library that offers higher-level access to the HPM. The second is to propose a new hardware/software system that offers more in-depth detail of the processor's state when profiling an application and presents a proof-of-concept implementation of it.

## 1.2 Contributions

This work hopes to offer to the RISC-V community the following contributions:

- Port the PAPI library to RISC-V while providing support for the SiFive U74-MC processor;

- Explanation of what steps need to be replicated or changed if PAPI support for new RISC-V

processors is desired;

- Proposal of a Precise Event Sampling (PES) facility inside of RISC-V's HPM that could be integrated into PAPI;

- Minimum viable implementation of a PES facility on a CVA6 processor.

## 1.3 Document Outline

This dissertation will continue with the background and state-of-the-art in Chapter 2, where the concepts and background knowledge necessary to understand the work developed are presented, as well as modern uses and techniques for HPMs. Then, in Chapter 3, the changes necessary to port the *PAPI* library to RISC-V are discussed and the results of the implementation are presented and analyzed. After, Chapter 4 goes over the design, implementation, results and shortcomings of a proof-of-concept PES facility for RISC-V processors. Finally, Chapter 5 wraps up the document with the achieved contributions and future work.

# **CHAPTER 2**

# **Background and State-Of-The-Art**

Following the objectives exposed in Section 1.1, the bulk of this work will revolve around HPM implementations on RISC-V processors and how the information obtained through them can be used to aid the development of more efficient software that fully utilizes the resources available to it.

Hence, this chapter describes the current state-of-the-art uses of hardware performance counters and the background to understand how they are defined in the context of RISC-V, how they are implemented, and modern tools to access them when using a Linux-based operating system.

In practice, Sections 2.1, 2.2 and 2.3 focus on the RISC-V definition for HPMs, the SiFive U7 implementation of HPM and the OpenHardware Group CVA6 implementation of HPM, respectively. Section 2.4 reviews some current developments on how Hardware Performance Counters are being improved. Sections 2.5 and 2.6 go over modern software that simplifies access to the HPM facilities in a processor. Section 2.7 explains how PES can be used to generate more useful information by studying how Intel PEBS and AMD IBS work.

## 2.1 RISC-V ISA

RISC-V [26], [27] is an open source ISA that was designed to support computer architecture research and education and also to become a free and open standard for industry implementations. The RISC-V ISA is purposely defined without implementation details to guarantee freedom for the vendor to adapt an architecture implementation to its needs.

This subsection will start with an overview of what the base RISC-V integer ISA is and the standard extensions available and defined by the RISC-V Foundation. Then, the specification given for a RISC-V HPM in [27] is run through.

## 2.1.1 Base Integer ISA and Extensions

A RISC-V ISA is defined as a base integer ISA, that is required for all implementations, in conjunction with optional extensions. The base integer ISA is meant to offer sufficient functionality for custom accelerators and educational purposes. Together with standard extensions, it can become an ISA suitable for more advanced computing and even general-purpose and high-performance computing. For this reason, and although RISC-V is usually referred to as a single ISA, it is a family of related ISAs. RISC-V ISAs are named based on a code that identifies the specific base ISA: "RV" followed by a number that indicates the length of the address space and either the letter "I", which indicates the existence of the standard number of 32 general purpose registers, or the letter "E", that stands for embedded and means that the only 16 general purpose registers exist. Additionally, a variety of letters can be concatenated to the end of the base name to indicate the ISA extensions present in the specific implementation. The address space length is also referred to as MXLEN (i.e., an RV64 system has MXLEN=64 and an RV32 system has MXLEN=32).

## 2.1.2 Hardware Performance Monitor

As mentioned in Section 2.1, the RISC-V specification does not provide implementation details. With this in mind, the present subsection goes over the general definition for a RISC-V HPM as described in [27]. Later sections will go over specific implementations of HPMs for the cores used in the development and testing of this thesis.

The HPM specification was first introduced in version 1.7 of the privileged specification and had the most recent change introduced in version 1.11 of the same document.

### **Fixed And Programmable Event Counters**

The counters available in RISC-V HPM are: mcycle that counts the number of executed cycles in the core, minstret that counts the number of retired instructions and an additional 29 programmable event counters mhpmcounter3-mhpmcounter31. All of these counters are machine-level read and write Control Status Registers (CSRs) and have 64-bit precision in both RV64 and RV32 systems.

Event selector CSRs mhpmevent3-mhpmevent31 are MXLEN-bit wide registers that are used to control which event is being counted on the corresponding counter (e.g., mhpmevent3 controls the event that causes mhpmcounter3 to increment). The meaning of the programmable events and their encoding should be defined by the vendor of the specific implementation except event 0 which always means "no event". The specification indicates that all 29 programmable counters and their respective event selectors should be implemented while also stating a valid implementation is to make unused programmable counters and their respective selectors read-only 0.

As previously stated, the programmable event counters always have 64-bit precision. To comply with this in RV32 access to 64-bit registers is made in two steps: reads/writes of mcycle, minstret and mhpmevent3-mhpmevent31 return/change only bits 31-0 and reads/writes of mcycleh, minstreth and mhpmevent3h-mhpmevent31h return/change bits 63-32.

### **Counter Availability To Lower Privilege Levels**

The mcycle, minstret and mhpmevent3-mhpmevent31 registers are machine-level read and write CSRs, meaning reads/writes from lower privilege levels will trigger an illegal instruction exception. The cycle, instret and hpmevent3-hpmevent31 CSRs are read-only shadows of mcycle, minstret and mhpmevent3-mhpmevent31. Their availability to the next implemented privilege level is controlled through the mcounteren CSR. The mcounteren is a 32-bit register and is organized in a one-hot encoding of all hardware performance counters plus the memory-mapped mtime register, as shown in Figure 2.1. As an example, when bit 0 is clear, reads of cycle from a privileged mode lower than machine mode will generate an illegal instruction exception. When bit 0 is set, access for reads is permitted to the next implemented privilege mode (i.e., supervisor-mode if implemented or user-mode otherwise).

The mcounteren must always be implemented if the system implements user-mode but it may be set to read-only 0.

| 51    | 30    | 29    | 20                                 | 0   | 5       | 4                     | 3    | 2      | 1  | 0  |

|-------|-------|-------|------------------------------------|-----|---------|-----------------------|------|--------|----|----|

| HPM31 | HPM30 | HPM29 |                                    |     | HPM5    | HPM4                  | HPM3 | IR     | TM | CY |

| 1     | 1     | 1     | 23                                 |     | 1       | 1                     | 1    | 1      | 1  | 1  |

|       |       |       |                                    |     |         |                       |      |        |    |    |

|       |       | Fig   | ure 2.1: Counter-enable register m | COL | Interen | , <mark>[27</mark> ]. |      |        |    |    |

|       |       | •     | C C                                |     |         |                       |      |        |    |    |

| 31    | 30    | 29    | 28                                 | 6   | 5       | 4                     | 3    | 2      | 1  | 0  |

| HPM31 | HPM30 | HPM29 |                                    |     | HPM5    | HPM4                  | HPM: | 3   IR | 0  | CY |

| 1     | 1     | 1     | 23                                 |     | 1       | 1                     | 1    | 1      | 1  | 1  |

6

## **Counter Inhibition**

21

30

20

90

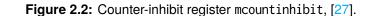

The counter-inhibit register mcountinhibit is a 32-bit register that controls whether a hardware performance counter increments when the programmed event occurs or not. It is implemented using a one-hot encoding of the available counters, as shown in Figure 2.2. As an example, when bit 0 of mcountinhibit is clear, the mcycle register will increment normally. When bit 0 of mcountinhibit is set, mcycle register will not increment.

The mcountinhibit register can not be implemented and, in that case, the implementation should behave as if the register were set to read-only 0.

## **Overflow Or Threshold Handling**

At the time of writing, no specification for a mechanism that generates an interrupt when an HPM counter overflows or reaches a previously chosen threshold exists.

#### SiFive U7 Core 2.2

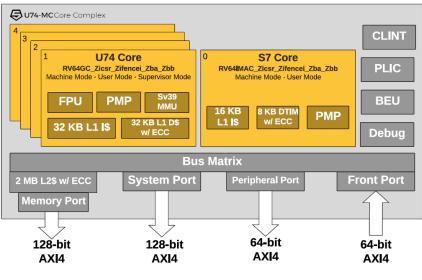

The U7 core was designed by SiFive and is included in the U74-MC core complex [23]. A block diagram of U74-MC is presented in Figure 2.3. Its ISA is RV64IMAFDC, which means, a base RISC-V integer ISA with a 64bit address space that also has the standard extensions: "M" (integer multiplication), "A" (atomic instructions), "F" (single-precision floating-point), "D" (double-precision floating-point) and "C" (compressed instructions). The standard instructions "M", "A", "F" and "D" are often bundled together into the single denomination "G", as they are essential for a general-purpose microprocessor.

The U7 core processor core implements a basic HPM that is divided into two classes of counters: fixed-function counters and event programmable counters.

#### 2.2.1 **Fixed-Function Performance Monitoring Counters**

The fixed class of counters consists of a set of fixed counters and their corresponding counter-enable registers. As the name indicates, a fixed-function performance monitor counter is hardwired to one specific event and that event cannot be changed. The only flexibility provided by this class of counters is the ability to enable or disable the counting through the counter-enable registers and to change the counter value.

Figure 2.3: U74-MC Series Block Diagram [23]

The following fixed-function counters are provided in the U74-MC core:

## mcycle

The fixed-function performance monitoring counter mcycle holds the count for the number of clock cycles executed since an arbitrary time in the past. It is 64 bits wide and reading the CSR will return all 64 bits.

### minstret

Likewise, the fixed-function performance monitoring counter minstret holds the count of the number of instructions retired since an arbitrary time in the past. The counter is 64 bits wide and reading the CSR will return all 64 bits.

This implementation of the fixed-function performance monitor counters corresponds with the requirements defined by the RISC-V Foundation in [27].

## 2.2.2 Event-Programmable Performance Monitoring Counters

The programmable class of counters is composed of event-programmable counters and event-selector registers. The U7 HPM boasts two of these counters: mhpmcounter3 and mhpmcounter4. They are implemented as 40-bit counters and can be written to initialize their count value. To control the event being counted by the programmable counters, two event-selector CSRs are provided: mhpmevent3 and mhpmevent4. These CSRs are 64-bit wide and are partitioned into three fields (as shown in Figure 2.4), with the 8 least significant bits representing the event class; bits 8 through 55 forming a mask for the events in said class; bits 56 and 57 are reserved and do not currently have an associated functionality; bits 58 through 62 inhibit the count of events when the core is in the associated privilege level (refer to Table 2.1 for specific privilege level related to each bit), which means that if all are set to zero, the count

| Name     | Attr                                                                 |                                                                                              |

|----------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

|          | Altr                                                                 | Description                                                                                  |

| Class    | WARL                                                                 | Selects the Event Class to make available for counting                                       |

| EventSel | WARL                                                                 | Bit-mask of Event(s) to count                                                                |

| Reserved | -                                                                    |                                                                                              |

| VUINH    | WARL                                                                 | Reserved                                                                                     |

| VSINH    | WARL                                                                 | Reserved                                                                                     |

| UINH     | WARL                                                                 | If set, counting of events in U-mode is inhibited                                            |

| SINH     | WARL                                                                 | If set, counting of events in S-mode is inhibited                                            |

| MINH     | RW                                                                   | If set, then counting of events in M-mode is inhibited                                       |

| OF       | RW                                                                   | Overflow status and interrupt disable bit. Set by hardware when counter overflows.           |

| R        | EventSel<br>leserved<br>VUINH<br>VSINH<br>UINH<br>SINH<br>MINH<br>OF | EventSel WARL<br>leserved -<br>VUINH WARL<br>VSINH WARL<br>UINH WARL<br>SINH WARL<br>MINH RW |

Table 2.1: mhpmeventX Register bit layout for overflow and filtering [23].

occurs in all privilege levels; and bit 63 indicates whether the associated counter as overflown and in such case remains set until it is written by software.

According to the RISC-V Foundation [27], the programmable counters mhpmcounter5 through mhpmcounter31 must also physically exist in the processor but is a legal implementation to have both the unused counters and their corresponding event selector CSR be read-only zero registers.

In Section 2.2.3 an explanation of how the events are encoded into the mhpmeventX CSR is presented and an example is given.

| 63   | 5655          | 8 7               | 0           |

|------|---------------|-------------------|-------------|

| Over | flow + Filter | Event Mask [55:8] | Event Class |

|      |               |                   |             |

Figure 2.4: Event selector fields [23].

## 2.2.3 Event Selector Encodings

On the U7 core, events are categorized into classes, which are selected by setting the correct bits in the mhpmeventX CSR. Specific events are selected by setting the corresponding bit on the Event Mask field of mhpmeventX. Multiple events from a given class can have their corresponding bit set on a given mhpmeventX. In that case, the count is incremented every time any of the selected events occurs. If all the bits in the Event Mask are set to 0, nothing is counted.

All the events available to program the two programmable counters, their class and their Event Mask encoding are present in Table 2.2. In the implementation of the U7 core used during the development of this work, setting a bit in the Event Mask that is not defined in the specified Event Class does not affect the count, but is discouraged as it might make software incompatible with future implementations that may expand the list of available events.

As a quick example: if the mhpmevent3 CSR is set to 0x4200 (activating solely bits 9 and 14), it can be verified by referencing Table 2.2 that mhpmcounter3 will increment every time either the events "Integer load instruction retired" or "Conditional branch retired" occur.

| Machine Hardware Performance Monitor Event Register |                                                           |  |  |  |  |  |  |

|-----------------------------------------------------|-----------------------------------------------------------|--|--|--|--|--|--|

|                                                     | Instruction Commit Events, <pre>mhpmeventX[7:0]=0x0</pre> |  |  |  |  |  |  |

| Bits                                                | Description                                               |  |  |  |  |  |  |

| 8                                                   | Exception taken                                           |  |  |  |  |  |  |

| 9                                                   | Integer load instruction retired                          |  |  |  |  |  |  |

| 10                                                  | Integer store instruction retired                         |  |  |  |  |  |  |

| 11                                                  | Atomic memory operation retired                           |  |  |  |  |  |  |

| 12                                                  | System instruction retired                                |  |  |  |  |  |  |

| 13                                                  | Integer arithmetic instruction retired                    |  |  |  |  |  |  |

| 14                                                  | Conditional branch retired                                |  |  |  |  |  |  |

| 15                                                  | JAL instruction retired                                   |  |  |  |  |  |  |

| 16                                                  | JALR instruction retired                                  |  |  |  |  |  |  |

| 17                                                  | Integer multiplication instruction retired                |  |  |  |  |  |  |

| 18                                                  | Integer division instruction retired                      |  |  |  |  |  |  |

| 19                                                  | Floating-point load instruction retired                   |  |  |  |  |  |  |

| 20                                                  | Floating-point store instruction retired                  |  |  |  |  |  |  |

| 21                                                  | Floating-point addition retired                           |  |  |  |  |  |  |

| 22                                                  | Floating-point multiplication retired                     |  |  |  |  |  |  |

| 23                                                  | Floating-point fused multiply-add retired                 |  |  |  |  |  |  |

| 24                                                  | Floating-point division or square-root retired            |  |  |  |  |  |  |

| 25                                                  | •                                                         |  |  |  |  |  |  |

|                                                     | Microarchitectural Events, mhpmeventX[7:0]=0x1            |  |  |  |  |  |  |

| Bits Description                                    |                                                           |  |  |  |  |  |  |

| 8                                                   | Address-generation interlock                              |  |  |  |  |  |  |

| 9                                                   | Long-latency interlock                                    |  |  |  |  |  |  |

| 10                                                  | CSR read interlock                                        |  |  |  |  |  |  |

| 11                                                  | Instruction cache/ITIM busy                               |  |  |  |  |  |  |

| 12                                                  | Data cache/DTIM busy                                      |  |  |  |  |  |  |

| 13                                                  | Branch direction misprediction                            |  |  |  |  |  |  |

| 14                                                  | Branch/jump target misprediction                          |  |  |  |  |  |  |

| 15                                                  | Pipeline flush from CSR write                             |  |  |  |  |  |  |

| 16                                                  | Pipeline flush from other event                           |  |  |  |  |  |  |

| 17                                                  | Integer multiplication interlock                          |  |  |  |  |  |  |

| 18                                                  | 18 Floating-point interlock                               |  |  |  |  |  |  |

|                                                     | Memory System Events, mhpmeventX[7:0]=0x2                 |  |  |  |  |  |  |

| Bits Description                                    |                                                           |  |  |  |  |  |  |

| 8                                                   | Instruction cache miss                                    |  |  |  |  |  |  |

| 9                                                   | <b>y</b> 11                                               |  |  |  |  |  |  |

| 10                                                  | Data cache write-back                                     |  |  |  |  |  |  |

| 11                                                  | Instruction TLB miss                                      |  |  |  |  |  |  |

| 12                                                  | Data TLB miss                                             |  |  |  |  |  |  |

| 13                                                  | UTLB miss                                                 |  |  |  |  |  |  |

Table 2.2: mhpmevent Register on SiFive U7 [23].

| Machir | Machine Hardware Performance Monitor Event Register |  |  |  |  |

|--------|-----------------------------------------------------|--|--|--|--|

| Value  | Description                                         |  |  |  |  |

| 0x1    | L1 I-Cache misses                                   |  |  |  |  |

| 0x2    | IL1 D-Cache misses                                  |  |  |  |  |

| 0x3    | ITLB misses                                         |  |  |  |  |

| 0x4    | DTLB misses                                         |  |  |  |  |

| 0x5    | Load accesses                                       |  |  |  |  |

| 0x6    | Store accesses                                      |  |  |  |  |

| 0x7    | Exceptions                                          |  |  |  |  |

| 0x8    | Exception handler returns                           |  |  |  |  |

| 0x9    | Branch instructions                                 |  |  |  |  |

| 0xA    | Branch mispredicts                                  |  |  |  |  |

| 0xB    | Branch exceptions                                   |  |  |  |  |

| 0xC    | Call                                                |  |  |  |  |

| 0xD    | Return                                              |  |  |  |  |

| 0xE    | MSB full                                            |  |  |  |  |

| 0xF    | Instruction fetch empty                             |  |  |  |  |

| 0x10   | L1 I-Cache accesses                                 |  |  |  |  |

| 0x11   | L1 D-Cache accesses                                 |  |  |  |  |

| 0x12   | Eviction                                            |  |  |  |  |

| 0x13   | I-TLB flush                                         |  |  |  |  |

| 0x14   | Integer instructions                                |  |  |  |  |

| 0x15   | Floating point instructions                         |  |  |  |  |

| 0x16   | Pipeline bubbles/Stall                              |  |  |  |  |

Table 2.3: mhpmevent Register on CVA6.

## 2.3 CVA6

Designed to provide insight into the energy cost and tradeoffs associated with projecting a RISC-V core with support for fully-fledged operating systems [33], CVA6 (previously known as Ariane), is a 6-stage, single-issue, in-order CPU that implements an RV64IMAFDC ISA. It supports the M, S and U RISC-V privilege modes, which allows compatibility with Unix-like operating systems.

## 2.3.1 Performance Monitoring Unit

Similarly to the implementation presented for the SiFive U7 core (Section 2.2), the CVA6 core implements the mcycle and minstret fixed counters, following the RISC-V privileged specification [27].

CVA6 implements 6 programmable counters, all of which can count all events but without the ability to multiplex the counters to more than 1 event at a time. The mhpmcounterX counters are programmed by setting the corresponding mhpmeventX CSR to the mask that encodes the desired event, with mhpmeventX set to 0 meaning no event is to be counted. All available events and their encoding are provided in Table 2.3.

Additionally, the HPM implementation includes the mcountinhibit CSR to allow for the counting to be halted in a specific counter, also following the most recent RISC-V privileged specification.

Figure 2.5: PLIC communication flow, [10]

## 2.3.2 Platform-Level Interrupt Controller

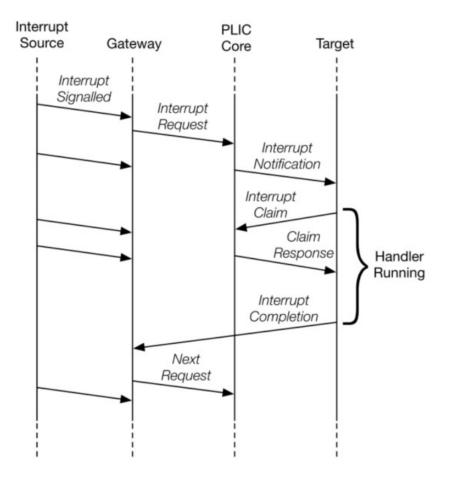

The PLIC included in the CVA6 processor follows the RISC-V International specification, [10], and is used in RISC-V computers to generate external interrupts that the cores can then handle.

The working of the PLIC can be divided into 4 steps. First, an interrupt source (like a keyboard or a signal coming from the core itself) activates letting the PLIC gateway know that the source device needs the core to handle something. The gateway then sends an interrupt request to the PLIC core, and if the Interrupt Enable for that source is set, the target for that external interrupt is not pending the resolution of a previous interrupt and the interrupt priority for the desired interrupt overcomes the currently defined priority threshold, the PLIC core sends an interrupt pending signal to the correct privilege mode of the target hart, or what the specification calls a context.

When the RISC-V core is notified that it has an interrupt pending it should read a specified memory location (as an example, the M mode of Hart 0 should write to the memory location base + 0x200004, with base meaning the PLIC base memory address which in CVA6 is 0xC000000). When the core finishes the execution of the interrupt handler, it should write the value it read before to that same memory address to let the PLIC know the handler has completed and the context is ready to receive external interrupts. The specification mentions that the value written is not verified so although the value written should be the same it will work even if it is not. This communication flow is illustrated in Figure 2.5.

## 2.4 Modern development on Hardware Performance Counters

## 2.4.1 Hardware Multiplexing

Due to the limited number of physical counters usually available in comparison with the number of selectable events to count on a processor (as an example, the SiFive U7 can count 35 different programmable events but only offers 2 programmable counters), in 2001 [15] proposed a novel way to count more than one event at a time in one programmable counter. The *MPX* method, as it was called, proposed that if the occurrence of an event *e* during a certain time *T* was fairly constant, the time *T* could be divided into equally long slots in which more than one event would be counted in round-robin fashion. The actual amount of times that *e* occurred would be approximately equal to the counted amount of *e* multiplied by the ratio between the total time *T* and the time event *e* was being counted. Or, in other words, *MXP* proposed that Hardware Performance Counters should be time-multiplexed. The results shown in the paper were positive, managing to have their prediction for four concurrent events stay within 5% of measurements done without multiplexing, in most cases. However, due to the inherent memory inefficiency of the software that controls *MXP*, demonstrated inaccuracies reach as high as 70% and there is no bound for how inaccurate a count can be due to the unknown consistency of the event occurrence.

In order to try and overcome these limitations, several solutions were proposed over the years and, in 2021, [32] suggested a paradigm shift from deterministic counters to an architecture based on approximate counting algorithms. This architectural philosophy allows for great reductions of memory usage, which was the *MXP*s Achilles' heel. As such, hardware events related to memory are more accurate when compared to the other method of time multiplexation. Also, the approximate algorithms counter approach has a theoretical maximum for relative error: 89%.

## 2.5 Perf\_events

As previously discussed, most modern processors include in their architecture some implementation of the concept of hardware performance monitoring through event counters. Often, direct access to these counters is restricted to code executing at the supervisor-level. To overcome this restriction, libraries that provide an interface between the user and the operating system kernel started emerging, like *Oprofile*, *Perfctr* or *Perfmon2*.

Until 2009, the Linux kernel did not ship with integrated support for performance counter access and all existing implementations had to be patched into the kernel. With the release of Linux kernel version 2.6.31, the *perf\_events* subsystem was introduced [30] as the default interface for accessing hardware performance counters. It was designed with functionality and abstraction in mind to make it simple to operate.

Unlike previously available interfaces, that used pseudo-filesystems or emulated devices to access the performance counters, *perf\_events* uses the perf\_event\_open() [11] system call to allocate file descriptors with the events to be counted specified at the open time in the fields of the perf\_event\_attr

[11] structure and counters can be enabled and disabled with ioctl() or prctl() system calls. As the communication with the kernel is done through file descriptors, a read() system call is used to read the values counted.

The perf\_event\_attr has a high number of variables and not all of them are relevant to this work. The ones that deserve the most attention in this context are:

### type

This variable specifies the general event type to be configured. It can take predefined values such as PERF\_TYPE\_HARDWARE if it is a general event provided by the kernel or PERF\_TYPE\_RAW if the user intends to use an implementation-specific event to configure the hardware performance counter.

### config

This variable specifies the actual event to be set. It works following the value set in the *type* variable to determine the event. Following the previous examples, if *type* is PERF\_TYPE\_HARDWARE, the user can select PERF\_COUNT\_HW\_CPU\_CYCLES to select an event that counts executed processor cycles for example; if *type* is PERF\_TYPE\_RAW, this variable needs to be set to a specific value determined by the vendor. The *libpfm4* library can be used to translate between event names and their hexadecimal encoding; more in Section 2.6.2.

The front-end of the *Perf\_events* subsystem is the *perf* [7] profiler. *perf* is especially well suited to conduct microprocessor analysis as it is capable of profiling processor stack traces, tracing CPU scheduler behaviors and probe performance monitoring counters.

In the context of this work, *Perf\_events* is used to interface with the performance monitoring counters of RISC-V processors. Every specific implementation of a processor has its configuration codes to indicate what hardware events should be counted by the programmable performance monitoring counter, like the codes discussed in Section 2.2.3. *perf* does not expect the user to know every single code a processor might have listed in its manual and provides human-readable mappings for supported processor implementations. As an example, instead of the user having to remember the code for counting exceptions taken on the SiFive U74-MC is (0x0100), they simply have to remember the event name "exception\_taken".

Full support for every event mappable in the SiFive U7 processor core is available on *Perf\_events* [3], a work previously developed within EPI.

## 2.6 Performance API - PAPI

Even when most processor platforms started adopting hardware performance monitoring counters in the late 1990s, access to them was still poorly documented, unstable and not available to user-level programs. These conditions made it difficult for performance tool developers to implement their solutions and for users to easily use such tools or to monitor and profile the processor usage of their applications. *PAPI* [1], [5], [25], [31] was created with the main focus of providing an easy-to-use set of interfaces that could gain access to the hardware performance counters of the major processor platforms. This could free developers of the unnecessary difficulties of obtaining such information to tune and optimize their software, run performance analysis or model the processor usage of their implemented solutions.

*PAPI* provides two interfaces to the hardware counters. One is a simple and high-level interface to acquire simple measurements and another is low-level and allows for more refined functionality. The high-level interface only allows the user to start, stop and read counters for a specified list of events. On the low-level interface, the user can manually manage the hardware event groups to be measured; which are called *EventSets*.

*PAPI* was also implemented with portability in mind. When a program is written using *PAPI* functions to profile its performance, that code should not have to be altered if it is to be used in another computer for which the architecture is supported by *PAPI* and it is installed.

## 2.6.1 Original Design

In this subsection, a brief discussion of how PAPI works is presented.

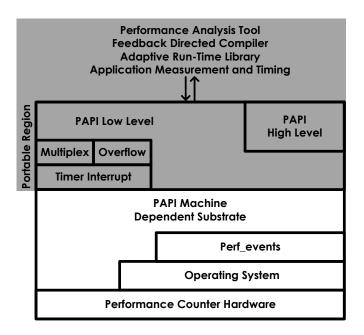

### Layers

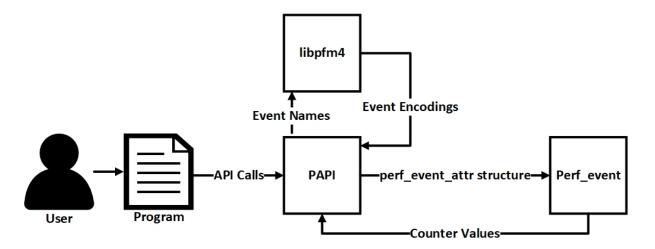

Figure 2.6 is a simple representation of *PAPI* layered approach. *PAPI* is internally split into two parts: a portable part and a machine-dependent part.

The portable part contains both the high and low-level interfaces and is independent of the architecture it is running on, so it does not require much work when porting *PAPI* to new implementations of already supported architectures. All the API functions and utilities that manage state handling, memory management, data structure manipulation and thread safety are defined here.

The machine-dependent code composes the internal *PAPI* layer and is denominated substrate. The portable layer calls function defined on the substrate as a means to access the hardware counters. Having its interface and functionality well defined but no implementation method specifics, the substrate can be easily updated and changed with no great incompatibilities. Any architecture/operating system combination needs only one new substrate layer to provide *PAPI* support.

## Portability

The *PAPI* API allows source code portability through a common interface, but it does not solve any problems related to decoding the machine-specific settings for accessing HPMs. To address this, *PAPI* defines a list of predefined events, or presets, that represent most of the events that are commonly used in a modern processor. Some of these events are, for example, total cycles, total instructions used, total branch instructions completed or floating-point instructions completed per second.

A *PAPI* substrate should implement as many presets as possible without providing misleading or wrong results. This simplification could potentially confuse if the same preset event is compared between different systems which may, of course, have distinct implementations for counting the specified event. As such, directly comparing two systems is not the intention of *PAPI* providing presets, but rather to introduce

Figure 2.6: PAPI architecture, modified from [1].

standard names for the metrics available. Because of this, it is still necessary for the user to possess a working knowledge of the system that they are testing to be able to correctly interpret the data collected with *PAPI*.

## **EventSets**

EventSets are used in *PAPI* as an abstraction from singular hardware events and are composed of events the user wishes to count as a group. Two major reasons are presented to follow this approach, one technical and one practical.

The first one is that aggregating events together increases efficiency when accessing counters through the operating system. Since most operating systems support using a single system call to move the value of more than one counter, grouping events greatly reduces the overhead of multiple system calls. This is especially important when *PAPI* is used to monitor small regions of code inside loops that iterate many times.

The second reason for the existence of EventSets is to allow users to create their counter groupings, catered to their specific application areas. The necessity for such groupings arises from the fact that in some instances, a singular event count is not enough to explain the performance of a certain region of code. Commonly, the more relevant information is only attainable by relating different metrics.

When using *PAPI*, the user is allowed to create as many EventSets as needed. Providing the substrate can provide the necessary resources. They are also allowed to use them simultaneously and share counters between them. If more events are added to the EventSet than are simultaneously countable by the HPM and the user has not explicitly enabled software multiplexing, an appropriate error is returned. An error is also returned if the user tries to use an EventSet improperly.

### Multiplexing

Although most modern processor architectures provide hardware performance counters, usually only a very small number of them are present, and consequently, the amount of events that can be counted at the same time is also low. This constraint means that the quantity of information acquirable in each run is sharply diminished and, in the eventuality that the application under study takes a long time to execute, the necessity to obtain various metrics might compound the run time of the test into several hours, days, or even weeks.

To avoid such limitation, *PAPI* subdivides the usage of counting hardware over time, or what is called multiplexing. By using multiplexing the user perceives that more hardware events are countable at the same time.

Although multiplexing incurs a small overhead and negatively affects the counting accuracy, the advantage of monitoring several metrics concurrently vastly outweighs the disadvantages. Even so, to prevent the user from unwittingly using multiplexing without being aware of the loss of precision, in both the low and high-level interfaces, it has to be activated manually with a specific API call.

## **Threshold Handling**

*PAPI* provides the user with the possibility to define handlers for when a specific hardware event surpasses a predetermined threshold. This functionality is implemented by using a high-resolution interval timer and setting a timer interrupt handler. If the system does not support counter overflow, *SIGPROF* and *ITIMER\_PROF* are used instead.

The handler is called from the signal context bundled with some arguments whenever the counter value is greater than the defined threshold. The user can then use the arguments given to determine the event that overflowed, by how much and where in the source code it happened.

PAPI uses the same functionality to handle counter value overflow.

### **Statistical Profiling**

The functionality of constructing statistical profiling of where a certain event count overflows is also offered by *PAPI*. It uses the method described in Section 2.6.1 to detect when the event surpasses the threshold and receives a signal that contains some arguments, namely: the stack pointer and program counter. Then it uses some underlying performance tool to get the address at which the program was interrupted and hash it into a histogram. At the end of the program execution, the user is given a line-by-line analysis of where the counter overflow happened. This study can be done with any implemented event.

To create a histogram of the type described, the user can use the PAPI\_profile() call.

### **Thread Support**

Since Symmetric Multiprocessing (SMP) was already popular in HPC applications by the time *PAPI* was created, thread awareness was part of its implementation since the beginning.

Being thread-aware implies that every globally writeable variable or structure is locked before it is modified and unlocked afterward. *PAPI* only has one global data structure to store process-wide options and thread-specific pointer maps. As this structure is only modified by two API calls and mostly at initialization or termination time of the *PAPI* library, assuring thread awareness does not represent a great overhead drawback when accessing hardware performance counters.

Another difficulty relates to the accuracy of the counters as, to be thread-aware, the operating system has to save and restore the HPM counters when context switching between active threads and processes. *PAPI* must also keep copies of every thread's counter data structure and values. *PAPI*s thread-awareness functionalities are only activated if more than one thread initializes the *PAPI* library or executes a *PAPI* API call.

Furthermore, some main-stream threading APIs don't explicitly present the concept of user-level or kernel-level threads to the user, like *Pthreads* and *OpenMPI*. In the case user-level threads are used, the values read are likely inaccurate and so, the user must explicitly bind the threads to kernel-level. In the HPC community this should not be of much concern as kernel-level threads are the standard.

#### **Counter Accuracy**

When *PAPI* was designed, it attempted to keep the overhead as small as possible to maintain disturbance to the performance analysis to a minimum. Even then, it is impossible to not contaminate the counter values at all and some inaccuracy can still occur due to other programs contending for the resources of the system or even because of the operating system background tasks.

In the original paper [1], the authors of *PAPI* did not provide any study on the accuracy of hardware performance counters or the *PAPI* library itself but [5] briefly refers to [12], where it is concluded that some accuracy problems when using hardware performance counters are prevalent when the granularity is used is too small to guaranty that the overhead of counting the events is not prevalent in the said count. The same study also found that the accuracy when attributing a hardware event to a specific instruction in out-of-order architectures is problematic.

In [30], it was shown that *PAPI* had a combined start, stop and read performance overhead of around 14000 cycles on an Intel Core 2 system, but also shows that further optimization is possible.

## 2.6.2 *libpfm4*

As mentioned in Section 2.6.1, the implementation of the substrate was not defined in the original *PAPI* specification and over the years, several approaches to access the hardware performance counters have been used. Since *PAPI* version 4, *libpfm4* has been used to communicate with *perf*, [28].

*libpfm4* [6] is a library used to develop monitoring tools that make use of performance monitoring events. This library can be used to convert an event name, given in a human-readable string, to a raw hardware event encoding compliant with the vendor specifications or to an OS-specific encoding, in which case it prepares the adequate data structure that the kernel requires. In the case of modern versions of *PAPI*, the events are set up through the kernel tool *perf*.

Figure 2.7: Basic structure for hardware performance counting using PAPI.

The data structure *perf* uses to interface with programs is the perf\_event\_attr [11] mentioned in Section 2.5.

## 2.6.3 How PAPI Reads Event Count Values

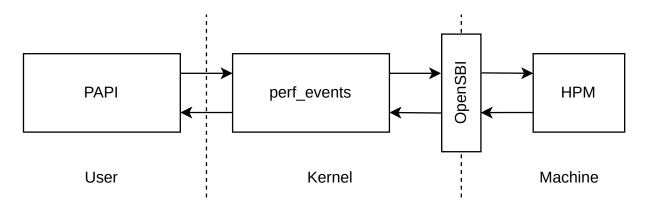

Summarizing all information in Section 2.6, what follows is a very brief explanation of how *PAPI* can be used to read hardware performance monitoring counter values. Figure 2.7 provides a visual representation of it.

The user writes a program and identifies what events they want to count to optimize or profile their software. They initialize the *PAPI* library and make the necessary API calls using event names in the form of human-readable strings. *PAPI*, in its most recent substrate version, inputs the Event name and machine-specific information to libpfm4, which translates this information into a perf\_event\_attr structure *perf* can use and gives this structure back to *PAPI*. The structure is then sent as an argument in a system call to the kernel's *perf\_events* subsystem. The return is a file descriptor *PAPI* utilizes to start, stop and read the counter values.

## 2.7 Precise Event Sampling

PES is a robust profiling technique supported by most modern processors HPMs that can sample hardware events and locate the instructions that trigger said events, [21]. It has been merged into modern software profiling tools to better identify performance bottlenecks and has been shown to enable the detection of inter-thread coherence traffic [20], false sharing [14], long latency remote memory accesses in NUMA multicore systems [13], data locality problems [22], performance degrading bandwidth consumption [8] and conflict cache misses [19]. Because this kind of sampling allows for the analysis of instruction pointers and addresses of data being operated, fully fleshed-out implementations of PES can help pinpoint bottlenecking instructions or data objects. Additionally, these tools offer lower time and memory overheads in comparison with options like cycle-accurate hardware simulators and it achieves this by sampling hardware information directly through implemented specialized hardware without adding much software

control.

This technology is already supported by major players like Intel *PEBS*, AMD *IBS*, IBM *MRK* and ARM *SPE*. They are not implemented in precisely the same way but all share similar characteristics, like the existence of specialized hardware on the HPM to enable PES. Currently, no RISC-V implementation has been presented in detail, having only been mentioned briefly in [2] as a means to other HPM uses.

In this section, an in-depth breakdown of Intel's *PEBS* is presented. This is the PES implementation presented because the proof-of-concept presented in this thesis for a RISC-V PES facility more closely follows Intel *PEBS* than the other mentioned implementations.

## 2.7.1 Intel PEBS

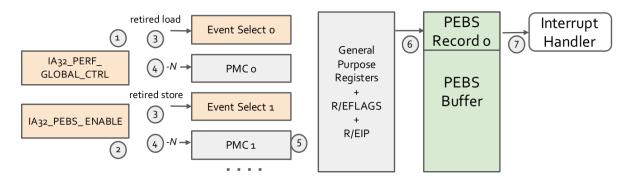

In Intel processors, since the Nehalem architecture, PES facilities have been present on Performance Monitoring Unit (PMUs) and can use all the programmable event counters available in them [9]. Intel PMU is governed by what are called global control registers. They can enable and disable both the event counters themselves (similar to the mcounteren CSR in RISC-V) as well as the PES functionality of each counter. To use PES, the global control registers are set so a programmable counter and its PES functionality are enabled, the corresponding event select register is programmed with the mask of the event the user wants to count and an overflow is defined so that every time the count in the counter reaches the predefined overflow, a sample is gathered. This number of events is also called the sampling period. When an overflow occurs, the PMU is rigged to capture the next occurrence of the event and when that happens, PEBS copies the machine state to a PEBS buffer in the form of PEBS records, what is called sampling. When the amount of PEBS records reaches a predefined amount, an interrupt is triggered so that the profiling software can retrieve the recorded information. This process is exemplified in Figure 2.8 for the case where retired load and store instructions are being profiled. The process works as follows: (1) Global control register IA32\_PERF\_GLOBAL\_CTRL enables PMC0 and PMC1 by setting its bits corresponding to both counters to one; (2) Global control register IA32\_PEBS\_ENABLE enables PEBS in PMC0 and PMC1 by setting the bits corresponding to both counters to one; (3) The event select registers IA32\_PERFEVTSEL0 and IA32\_PERFEVTSEL1 are programmed to make PMC0 and PMC1 count retired loads and retired stores, respectively; (4) The configured Perfomance Monitoring Counters (PMCs) are preloaded with the sampling interval, N, so that they overflow on elapsing N events. During execution, PMC1 counter overflows after N stores occur. Since PEBS is armed to trap the next store, PMC 1 is preloaded with N again. When another store occurs after the overflow PEBS traps the access and a microcode routine records the machine state in a PEBS buffer. If the number of records has reached a specified threshold (1 in this case), an interrupt is triggered, and an interrupt handler transfers the PEBS records to user space [21].

## 2.7.2 Precise Event Sampling Support in PAPI

As was discussed in Section 2.6.1, *PAPI* offers a simple event sampling functionality that records the overflow address and gives the user-defined handler the user thread context so it can also record any

Figure 2.8: One possible execution scenario of Intel PEBS. [21]

information accessible through it if it so wishes to.

Nevertheless, [29] identified the problems of this approach and proposed an integration of PES functionalities already present in modern processors, like *PEBS* and *IBS* as a way to solve them.

The paper highlights that the currently present statistical sampling implementation of *PAPI* incurs a greater overhead when compared to hardware/software PES systems because every overflow implies an interruption to store the overflow address and execute the user-defined handler function. The other identified problem is that through the user thread context made available to the user-defined handler, it is impossible to access higher-privileged level information, like kernel- and machine-level register states.

To overcome this issues, new *PAPI* interfaces are proposed, from which the one that would better integrate with *PEBS* would work by setting up existing **PES** facilities in the processors **HPM** and define an internal *PAPI* buffer that would be populated from the **PES** buffer when it was notified by the **HPM** to do so, via an interrupt. When the *PAPI* buffer fills up, a user-defined handler would be called to process the data or store it in a file.

## 2.8 Summary

The chapter begins by highlighting the central theme of hardware performance monitoring and PES.

The background section delves into the essential concepts of hardware performance monitoring. It outlines the significance of tracking a processor's performance and the role of event counters in this process. Special attention is given to RISC-V processors and their event counters.

Moving on to *PAPI*, this chapter elucidates its pivotal role as a versatile tool for accessing hardware performance counters. *PAPI* is presented as a valuable solution to the challenge of monitoring and profiling software execution efficiently.

The functionalities of *PAPI* are unveiled through its high-level and low-level interfaces. The high-level interface simplifies the process by allowing users to initiate, terminate, and retrieve counter data for a selected list of events. On the other hand, the low-level interface provides more fine-grained control by enabling users to manage event groups known as EventSets.

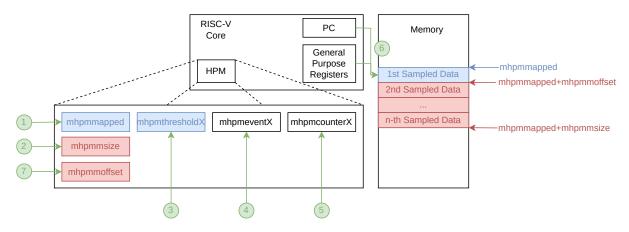

A core feature of *PAPI* is its portability, facilitating compatibility across different computer architectures. It ensures that code written with *PAPI* functions remains unaltered when transferred to another system supported by *PAPI*, emphasizing ease of use and cross-platform flexibility. The chapter touches on the concept of PES, a robust profiling technique. PES has gained prominence due to its ability to capture hardware events and identify the specific instructions or data operations responsible for these events.