# UNIVERSIDADE DE LISBOA INSTITUTO SUPERIOR TÉCNICO

# OPEN-END WINDING SYNCHRONOUS RELUCTANCE DRIVE BASED ON INDIRECT MATRIX CONVERTER WITH COMMON-MODE VOLTAGE REDUCTION

Alexandre Emanuel da Silva Bento

**Supervisor:** Doctor José Fernando Alves da Silva **Co-Supervisor:** Doctor Ricardo Jorge Ferreira Luís

> Thesis approved in public session to obtain the PhD Degree in Electrical and Computer Engineering Jury final classification: Pass with Distinction

# UNIVERSIDADE DE LISBOA INSTITUTO SUPERIOR TÉCNICO

# OPEN-END WINDING SYNCHRONOUS RELUCTANCE DRIVE BASED ON INDIRECT MATRIX CONVERTER WITH COMMON-MODE VOLTAGE REDUCTION

#### Alexandre Emanuel da Silva Bento

**Supervisor:** Doctor José Fernando Alves da Silva **Co-Supervisor:** Doctor Ricardo Jorge Ferreira Luís

> Thesis approved in public session to obtain the PhD Degree in Electrical and Computer Engineering Jury final classification: Pass with Distinction

#### Jury

Chairperson: Doctor Pedro Manuel Santos de Carvalho, Instituto Superior Técnico, Universidade de Lisboa

#### Members of the Committee:

Doctor José Fernando Alves da Silva, Instituto Superior Técnico, Universidade de Lisboa

Doctor Maria do Rosário Alves Calado, Faculdade de Engenharia, Universidade da Beira Interior

Doctor Sónia Maria Nunes dos Santos Paulo Ferreira Pinto, Instituto Superior Técnico, Universidade de Lisboa

Doutor Víctor Manuel de Carvalho Fernão Pires, Escola Superior de Tecnologia de Setúbal, Instituto Politécnico de Setúbal

#### **FUNDING INSTITUTION**

FCT - Fundação Para a Ciência e a Tecnologia

#### ACKNOWLEDGEMENTS

This work was supported by national funds through Fundação para a Ciência e Tecnologia (FCT) by an FCT PhD scholarship with reference SFRH/BD/129864/2017, by an FCT project PTDC/EEI-EEE/32550/2017, and by Instituto Politécnico de Lisboa within the scope of IDI&CA with project reference IPL/2018/GaN-SynRM\_ISEL. The thesis counted with INESC-ID, IST and ISEL as host institutions who ensured that the necessary conditions for the proper development of the work were met. A special thanks to the professors from ISEL Low Carbon Energy Conversion group for the permanent laboratory bench and all the provided equipment that were determinant for the laboratorial prototype.

I am extremely grateful to my supervisor Prof. Fernando Silva for his guidance, continuous support, almost infinite availability and will to share his valuable knowledge during this thesis.

I would also like to extend my deepest gratitude to my Co-supervisor Prof. Ricardo Luís for his guidance, continuous support and for the motivation given throughout the period we worked together, that ultimately led to pursuing this doctoral degree.

I am extremely grateful to Prof. Sónia Pinto that while not being a formal member of the supervising team, for sure has played an important part in it. Thank you Professor for your support and guidance during these years.

I would like to extend my deepest gratitude to my dearest friend Sérgio André, for his incredible availability, support and companionship that made the laboratorial prototype a reality. I wish you the best of luck with your own PhD.

To Paulo Almeida, thank you for continuing to play the triple role as a friend, a colleague, and a teacher that is always able to find a strangely easy solution to a given practical problem.

To my friends and PhD colleagues Pedro Costa and Guilherme Paraíso thank you for the friendship and companionship over the years and for great work environment on "sala 2.24" that I will for sure miss. I wish you the best of luck with your own PhD.

To my team for life, thank you Marisa Marques for being my rock over the years, that consistently gives me strength and confidence. To Duarte Bento, thank you for giving me the last bit of strength to end this PhD. I am deeply sorry that it stole part of our time together, thank you once again Marisa for securing our most precious treasure.

I will always be thankful to my parents and brothers for making me able to evolve personally and professionally, and for all their unconditional love and support.

To my good friends who are always my getaway from stress and problems, a big thank you and a wish of best luck for our new stages.

I finalize my acknowledgements with a very special thank you note to my grandfather Mário Silva for everything he has given and taught me all over the years. Everything I achieve will be with a little of his help.

Alexandre Bento, February 2023

#### ABSTRACT

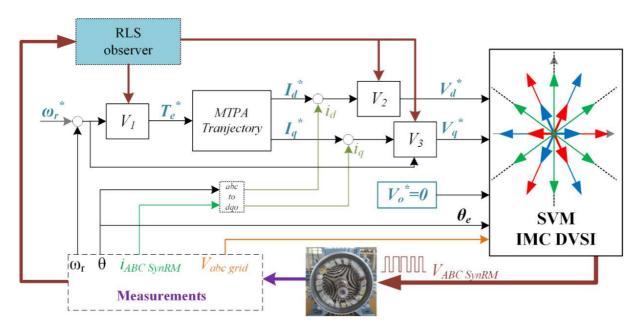

This thesis focus in two key parts of a variable speed drive: 1) the power electronics converter topology and modulation methods, and 2) on the electrical machine itself by developing a novel Adaptive Field-Oriented Controller for Synchronous Reluctance Machines.

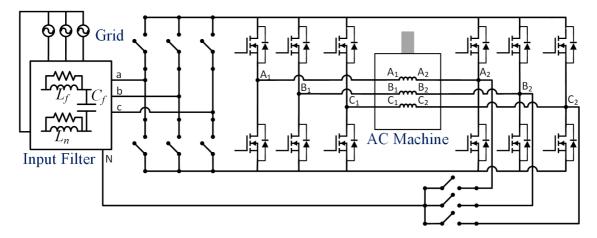

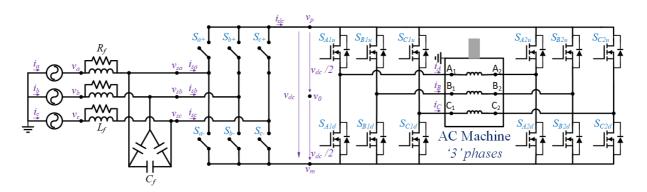

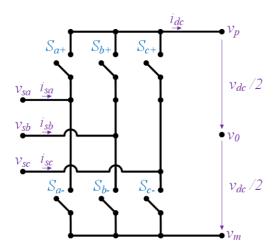

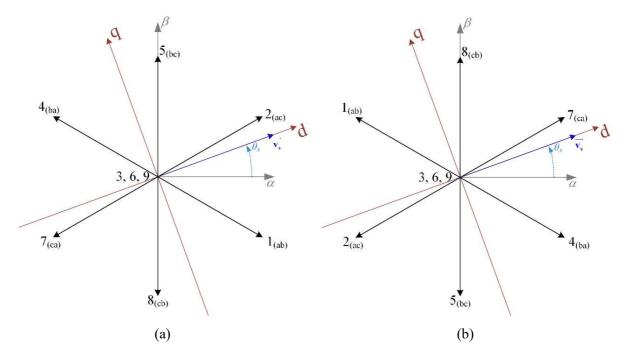

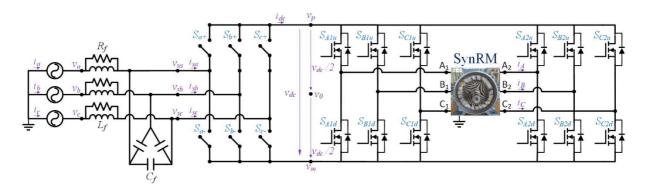

The power electronics converter topology under study combines an Indirect Matrix Converter with the Open-End Winding configuration of electrical machines. Such topology allows higher power density drives due to elimination of the intermediate dc-link energy storage electrolytic capacitors, which are one of the bulkier and lower lifetime components of traditional variable speed drive converters. Simultaneously by connecting the electrical machine in an Open-End Winding configuration, the Matrix converter voltage gain is increased to 1.5 eliminating one of the most prominent drawbacks, the low voltage gain, when using traditional Matrix converters to supply electrical machines. This thesis proposes a space vector modulation method for the Indirect Matrix Converter with a Dual Voltage Source Inverter output capable of reducing the Common Mode Voltage supplied to the electrical machine while improving input and output waveforms quality. In the situation where the modulated input power factor is unity, the proposed modulation method even eliminates the need for complex multistep commutation methods for switching the input stage bidirectional switches.

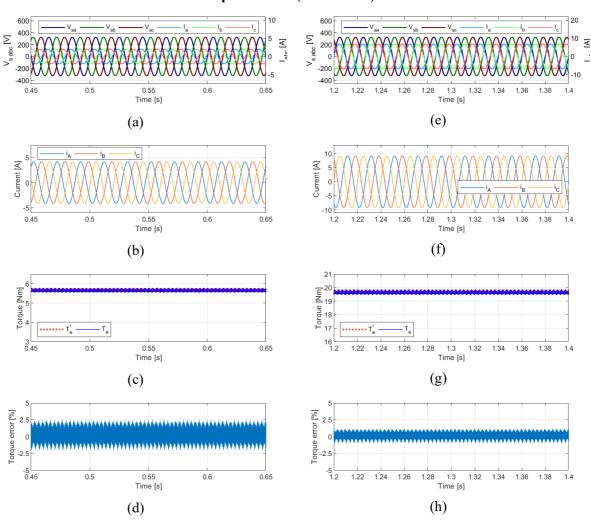

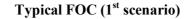

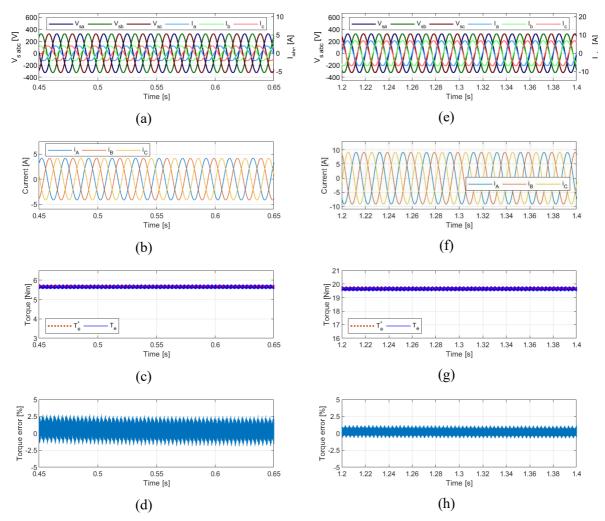

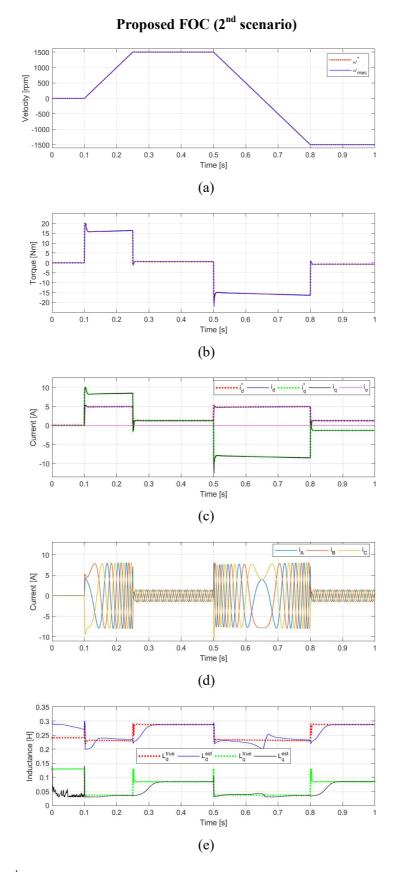

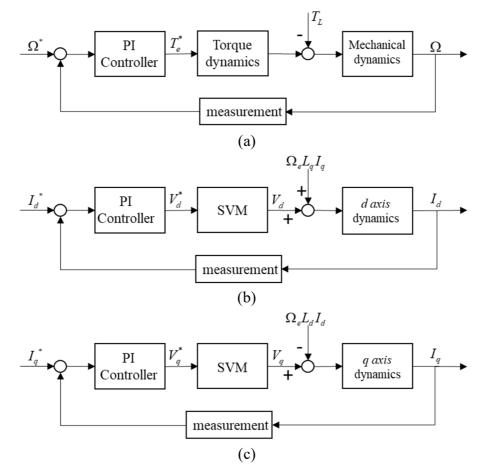

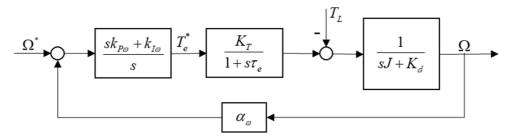

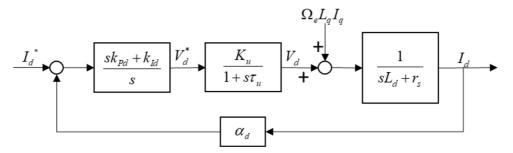

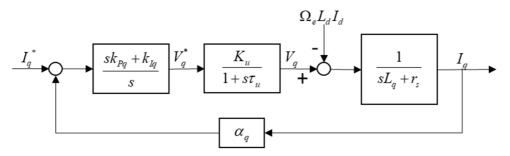

Regarding the control of the electrical machine, field-oriented controllers are often characterized as performing extremely well in steady state, showing lower torque ripple than other control strategies while allowing fixed switching frequency facilitating filter design. However, field-oriented controllers show poor dynamic response when exposed to drive disturbances or rapidly varying setpoints due to delays introduced by the Proportional Integral (PI) controllers used in their internal control loops. The approach proposed in this thesis eliminates the PI controllers, replacing them by adaptive non-linear backstepping controllers, whose stability is guaranteed by the Lyapunov 2<sup>nd</sup> method of stability. When compared to the traditional field-oriented controller, the proposed modified controller shows similar steady state performance and better dynamic behaviour by improving the varying speed tracking capability while achieving faster and more accurate response to the mechanical load step changes. This allows the conservation of the best steady state performance typical of traditional field-oriented controllers while achieving improved dynamic characteristic.

## **KEYWORDS**

Indirect Matrix Converter; Open-End Windings; Synchronous Reluctance Machine; Common Mode Voltage reduction; Adaptive Field-Oriented Control

#### **Resumo**

Esta dissertação foca-se no estudo de acionamentos eletromecânicos de velocidade variável com elevada fiabilidade e densidade de potência. Assim, o trabalho concentra-se em duas componentes fundamentais deste tipo de acionamentos: 1) a topologia e modulação do conversor eletrónico de potência, 2) o controlo por orientação de campo de máquinas síncronas de relutância.

No que diz respeito ao conversor eletrónico de potência, a topologia em estudo combina o conceito de conversores matriciais indiretos com esquemas de ligação de cargas elétricas em *open-end winding*. Esta topologia permite obter densidades de potência mais elevadas que as configurações tradicionais devido à eliminação dos condensadores eletrolíticos tipicamente utilizados no barramento de corrente contínua para armazenamento de energia de curta duração, sendo estes um dos componentes mais volumosos e com menor vida útil dos conversores eletrónicos de potência. Simultaneamente, ao utilizar a máquina elétrica num esquema *open-end winding*, o ganho de tensão do conversor matricial é aumentado para 1,5 face ao típico 0,866. Nesta dissertação, propõe-se um método de modulação por vetores espaciais para o conversor matricial indireto para cargas *open-end winding*. Este método consegue reduzir a tensão de modo comum injetada na máquina elétrica enquanto melhora a qualidade das formas de onda de entrada e saída do conversor. Na situação em que se pretende fator de potência de entrada unitário, o método de modulação elimina ainda a necessidade de métodos complexos de comutação em múltiplas etapas para a comutação dos interruptores bidirecionais do estágio de entrada.

Relativamente ao controlo da máquina síncrona de relutância, os controladores por orientação de campo são frequentemente caracterizados por terem um muito bom desempenho em regime permanente comparativamente a outras estratégias de controlo por apresentarem menor ondulação de binário e permitirem funcionamento a frequência de comutação fixa facilitando o projeto do filtro de entrada. Por outro lado, os controladores por orientação de campo são comummente criticados devido a proporcionarem respostas lentas aquando variações abruptas de carga ou de referências de velocidade devido aos atrasos introduzidos pelos controladores proporcionais integrais utilizados nas suas cadeias de controlo. A abordagem proposta neste trabalho consiste na substituição dos controladores proporcionais integrais por controladores adaptativos não lineares com *backstepping*, cuja estabilidade é garantida pelo segundo método de estabilidade de Lyapunov. Quando comparado com os controladores por orientação de

campo tradicionais, o controlador proposto consegue manter o excelente desempenho em regime permanente, enquanto permite obter uma melhoria significativa na performance dinâmica do acionamento de velocidade variável, apresentando melhores resultados em cenários de seguimento de referências de velocidade e em variações abruptas da carga mecânica aplicada ao eixo da máquina.

#### **PALAVRAS-CHAVE**

Conversor Matricial Indireto; Open-End Winding; Máquina Síncrona de Relutância; Tensão de Modo Comum; Controlo por Orientação de Campo Adaptativo

## SYMBOL TABLE

# Symbols

| U                                                                     |                                                                                                                                                           |

|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| b                                                                     | SynRM viscous friction coefficient divided by SynRM constant of inertia                                                                                   |

| CMV                                                                   | Common Mode Voltage at the IMC output                                                                                                                     |

| $C_{f}$                                                               | IMC input filter capacitance (delta connection)                                                                                                           |

| С                                                                     | Power Invariant Concordia Transformation                                                                                                                  |

| d                                                                     | SynRM mechanical load torque divided by SynRM constant of inertia                                                                                         |

| $e_{\omega}$                                                          | SynRM speed error                                                                                                                                         |

| eı                                                                    | Integral of SynRM speed error in time                                                                                                                     |

| $e_T$                                                                 | SynRM electromagnetic torque error                                                                                                                        |

| $e_d$                                                                 | SynRM d axis current error                                                                                                                                |

| $e_q$                                                                 | SynRM $q$ axis current error                                                                                                                              |

| $E^{R}_{sw}$                                                          | Energy lost due to one switching (turn ON and turn OFF) obtained from catalogue at reference voltage ( $V^{R}$ ) and current ( $I^{R}$ ) for the GaN HEMT |

| $E_{sw}$                                                              | Energy lost due to one switching (turn ON and turn OFF) for the GaN HEMT                                                                                  |

| $I^R$                                                                 | Reference current $(I^R)$ for the GaN HEMT obtained from the manufacturer catalogue for computation of Energy lost due to one switching                   |

| <i>i</i> <sub>A</sub> , <i>i</i> <sub>B</sub> , <i>i</i> <sub>C</sub> | IMC output currents                                                                                                                                       |

| $i_d$ , $i_q$ , $i_z$                                                 | SynRM stator currents in the dqz rotor reference frame                                                                                                    |

| io                                                                    | IMC output current vector                                                                                                                                 |

| $i_a$ , $i_b$ , $i_c$                                                 | Electrical grid currents                                                                                                                                  |

| isa, isb, isc                                                         | IMC input currents                                                                                                                                        |

| $i_{dc}$                                                              | IMC soft dc-link current                                                                                                                                  |

| J                                                                     | SynRM constant of inertia                                                                                                                                 |

| $k_D$                                                                 | SynRM viscous friction coefficient                                                                                                                        |

| $k_{\omega}$                                                          | Proportional gain of the Proposed Lyapunov speed controller                                                                                               |

| $k_I$                                                                 | Integral gain of the Proposed Lyapunov speed controller                                                                                                   |

| $k_d$                                                                 | Proportional gain of the Proposed Lyapunov d axis current controller                                                                                      |

| $k_q$                                                                 | Proportional gain of the Proposed Lyapunov $q$ axis current controller                                                                                    |

| $L_d$ , $L_q$ , $L_z$                                                 | SynRM inductances in the dqz rotor reference frame                                                                                                        |

| $L_{lk}$                                                              | SynRM leakage inductance                                                                                                                                  |

| $L_{f}$                                                               | IMC input filter inductance                                                                                                                               |

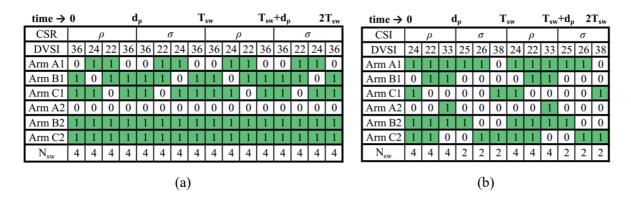

| $N_{sw}$                                                              | IMC output stage upper switches turned ON                                                                                                                 |

|                                                                       |                                                                                                                                                           |

| p                                                                                                                  | SynRM number of pole pairs                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| $P_{_{SW}}$                                                                                                        | IMC switching losses                                                                                                                                |

| $P_{cond}^{CSR}$                                                                                                   | IMC input stage conduction losses                                                                                                                   |

| $P_{cond}^{DVSI}$                                                                                                  | IMC output stage conduction losses                                                                                                                  |

| $R_{f}$                                                                                                            | IMC input filter damping resistor                                                                                                                   |

| $R_{ds}$                                                                                                           | Drain to Source resistance of the GaN HEMT device                                                                                                   |

| $R_s$                                                                                                              | SynRM stator winding resistances                                                                                                                    |

| $S_{a+}, S_{b+}, S_{c+}$                                                                                           | State of the IMC input stage upper bidirectional switches                                                                                           |

| S <sub>a-</sub> , S <sub>b-</sub> , S <sub>c-</sub>                                                                | State of the IMC input stage lower bidirectional switches                                                                                           |

| S <sub>CSR</sub>                                                                                                   | IMC input stage switching states matrix                                                                                                             |

| Sdvsi                                                                                                              | IMC output stage switching matrix                                                                                                                   |

| S <sub>A1u</sub> , S <sub>B1u</sub> , S <sub>C1u</sub> ,<br>S <sub>A2u</sub> , S <sub>B2u</sub> , S <sub>C2u</sub> | State of the IMC output stage upper semiconductors                                                                                                  |

| Said, Sbid, Scid,<br>Said, Sbid, Scid                                                                              | State of the IMC output stage lower semiconductors                                                                                                  |

| T <sub>e</sub>                                                                                                     | SynRM electromagnetic torque                                                                                                                        |

| $T_{load}$                                                                                                         | SynRM mechanical load torque                                                                                                                        |

| Trls                                                                                                               | RLS algorithm sampling time                                                                                                                         |

| $T_s$                                                                                                              | Simulation time step                                                                                                                                |

| $T_{sw}$                                                                                                           | SVM switching period                                                                                                                                |

| $V_0$                                                                                                              | Lyapunov function for speed control without load torque estimation                                                                                  |

| $V_1$                                                                                                              | Lyapunov function for speed control with load torque estimation                                                                                     |

| $V_2$                                                                                                              | Lyapunov function for $q$ axis current control with backstepping                                                                                    |

| $V_3$                                                                                                              | Lyapunov function for $d$ axis current control with backstepping                                                                                    |

| $V^R$                                                                                                              | Reference voltage $(V^{\mathcal{R}})$ for the GaN HEMT obtained from the manufacturer catalogue for computation of Energy lost due to one switching |

| V <sub>A1</sub> , V <sub>A2</sub> , V <sub>B1</sub> , V <sub>B2</sub> ,<br>V <sub>C1</sub> , V <sub>C2</sub>       | IMC output arm voltages to ground                                                                                                                   |

| VA10, VA20, VB10,<br>VB20, VC10, VC20                                                                              | IMC output arm voltages to the dc-link midpoint                                                                                                     |

| $v_a$ , $v_b$ , $v_c$                                                                                              | Electrical grid phase to ground voltages                                                                                                            |

| <i>VA</i> , <i>VB</i> , <i>VC</i>                                                                                  | IMC output phase voltages                                                                                                                           |

| Vo                                                                                                                 | IMC output voltage vector                                                                                                                           |

| V <sub>o</sub> *                                                                                                   | IMC output voltage reference vector                                                                                                                 |

| $V_d$ , $V_q$ , $V_z$                                                                                              | SynRM stator voltages in the dqz rotor reference frame                                                                                              |

| Vsa, Vsb, Vsc                                                                                                      | IMC input phase to ground voltages                                                                                                                  |

|                                                                                                                    |                                                                                                                                                     |

| Vsd, Vsq, Vsz                                                                                                                         | IMC input voltages in the $dqz$ reference frame, synchronized with $\theta_s$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{ph\ rms}$                                                                                                                         | IMC root mean square value phase-to-phase input voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Vdc                                                                                                                                   | IMC soft dc-link instantaneous voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| V <sub>dc</sub>                                                                                                                       | IMC soft dc-link average voltage during a full switching cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| $v_p$                                                                                                                                 | IMC dc-link 'p' busbar to ground voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $\mathcal{V}_m$                                                                                                                       | IMC dc-link 'm' busbar to ground voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $\mathcal{V}_0$                                                                                                                       | IMC soft dc-link midpoint to ground voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| $\mathcal{V}_G$                                                                                                                       | Instalation ground voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| $\mathcal{V}0G$                                                                                                                       | IMC input stage contribution to Common Mode Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| V <sub>cm0</sub>                                                                                                                      | IMC output stage contribution to Common Mode Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| $lpha_i$                                                                                                                              | SynRM current angle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| α, β, γ                                                                                                                               | Unitary vectors of the Concordia reference frame                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| γd                                                                                                                                    | Lyapunov controller gain for mechanical load torque estimation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| δ                                                                                                                                     | SynRM load angle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

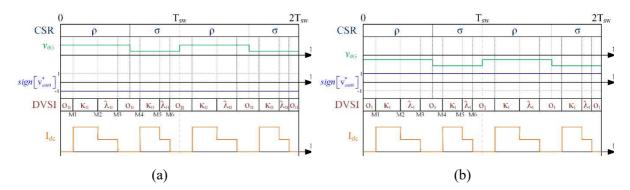

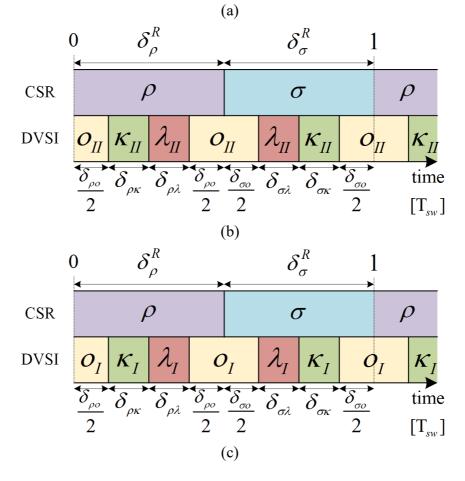

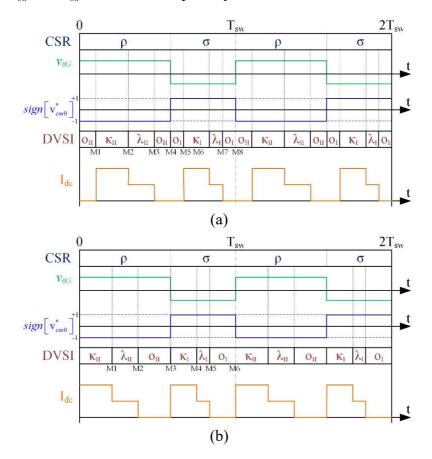

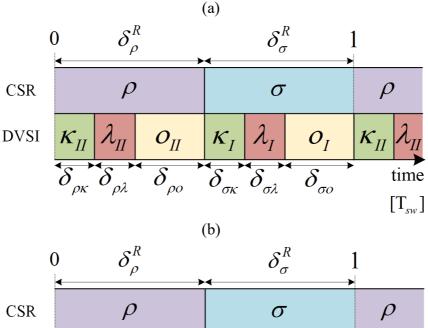

| $\delta^{\scriptscriptstyle R}_{\scriptscriptstyle  ho}$ , $\delta^{\scriptscriptstyle R}_{\sigma}$                                   | IMC input stage duty cycles for vectors $\rho$ and $\sigma$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| $egin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                    | IMC output stage duty cycles for vectors $\kappa$ , $\lambda$ , $o$ , $o1$ and $o2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 01 7 02                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ζ                                                                                                                                     | Damping ratio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                       | Damping ratio<br>SynRM rotor angle in respect to stator phase <i>a</i> winding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ζ                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| $\zeta \\ 	heta_m$                                                                                                                    | SynRM rotor angle in respect to stator phase <i>a</i> winding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| $\zeta$<br>$	heta_m$<br>$	heta_e$                                                                                                     | SynRM rotor angle in respect to stator phase <i>a</i> winding<br>SynRM electrical angle in respect to stator phase <i>a</i> winding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| $\zeta$<br>$	heta_m$<br>$	heta_e$<br>$	heta_i$                                                                                        | SynRM rotor angle in respect to stator phase <i>a</i> winding<br>SynRM electrical angle in respect to stator phase <i>a</i> winding<br>CSR input current phase reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $\zeta$<br>$	heta_m$<br>$	heta_e$<br>$	heta_i$<br>$	heta_s$                                                                           | SynRM rotor angle in respect to stator phase <i>a</i> winding<br>SynRM electrical angle in respect to stator phase <i>a</i> winding<br>CSR input current phase reference<br>CSR input voltages phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| $\zeta$<br>$	heta_m$<br>$	heta_e$<br>$	heta_i$<br>$	heta_s$<br>$\kappa$                                                               | SynRM rotor angle in respect to stator phase a windingSynRM electrical angle in respect to stator phase a windingCSR input current phase referenceCSR input voltages phaseIMC output stage Active vector applied first in the SVM switching periodIMC output stage Active vector applied second in the SVM switching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| $\zeta$<br>$	heta_m$<br>$	heta_e$<br>$	heta_i$<br>$	heta_s$<br>$\kappa$<br>$\lambda$                                                  | SynRM rotor angle in respect to stator phase <i>a</i> winding<br>SynRM electrical angle in respect to stator phase <i>a</i> winding<br>CSR input current phase reference<br>CSR input voltages phase<br>IMC output stage Active vector applied first in the SVM switching period<br>IMC output stage Active vector applied second in the SVM switching<br>period                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| $\zeta$<br>$	heta_m$<br>$	heta_e$<br>$	heta_i$<br>$	heta_s$<br>$\kappa$<br>$\lambda$<br>$\zeta$                                       | SynRM rotor angle in respect to stator phase a windingSynRM electrical angle in respect to stator phase a windingCSR input current phase referenceCSR input voltages phaseIMC output stage Active vector applied first in the SVM switching periodIMC output stage Active vector applied second in the SVM switchingperiodSynRM saliency ratioIMC output stage Null vector in the SVM switching period (DVSI group II                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| $\zeta$<br>$	heta_m$<br>$	heta_e$<br>$	heta_i$<br>$	heta_s$<br>$\kappa$<br>$\lambda$<br>$\zeta$<br>o                                  | SynRM rotor angle in respect to stator phase a windingSynRM electrical angle in respect to stator phase a windingCSR input current phase referenceCSR input voltages phaseIMC output stage Active vector applied first in the SVM switching periodIMC output stage Active vector applied second in the SVM switchingperiodSynRM saliency ratioIMC output stage Null vector in the SVM switching period (DVSI group IIvectors SVM strategy)IMC output stage Null vector applied first in the SVM switching period                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| $\begin{array}{l} \zeta \\ \theta_m \\ \theta_e \\ \theta_i \\ \theta_s \\ \kappa \\ \lambda \\ \xi \\ 0 \\ oldsymbol{1} \end{array}$ | <ul> <li>SynRM rotor angle in respect to stator phase <i>a</i> winding</li> <li>SynRM electrical angle in respect to stator phase <i>a</i> winding</li> <li>CSR input current phase reference</li> <li>CSR input voltages phase</li> <li>IMC output stage Active vector applied first in the SVM switching period</li> <li>IMC output stage Active vector applied second in the SVM switching period</li> <li>SynRM saliency ratio</li> <li>IMC output stage Null vector in the SVM switching period (DVSI group II vectors SVM strategy)</li> <li>IMC output stage Null vector applied first in the SVM switching period</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| $\begin{array}{c} \zeta \\ \theta_m \\ \theta_e \\ \theta_i \\ \theta_s \\ \kappa \\ \lambda \\ \zeta \\ 0 \\ 01 \\ 02 \end{array}$   | <ul> <li>SynRM rotor angle in respect to stator phase <i>a</i> winding</li> <li>SynRM electrical angle in respect to stator phase <i>a</i> winding</li> <li>CSR input current phase reference</li> <li>CSR input voltages phase</li> <li>IMC output stage Active vector applied first in the SVM switching period</li> <li>IMC output stage Active vector applied second in the SVM switching period</li> <li>SynRM saliency ratio</li> <li>IMC output stage Null vector in the SVM switching period (DVSI group II vectors SVM strategy)</li> <li>IMC output stage Null vector applied first in the SVM switching period (DVSI group I vectors SVM strategy)</li> <li>IMC output stage Null vector applied second in the SVM switching period (DVSI group I vectors SVM strategy)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| $\zeta$<br>$\theta_m$<br>$\theta_e$<br>$\theta_i$<br>$\theta_s$<br>$\kappa$<br>$\lambda$<br>$\zeta$<br>o<br>o1<br>o2<br>$\rho$        | <ul> <li>SynRM rotor angle in respect to stator phase <i>a</i> winding</li> <li>SynRM electrical angle in respect to stator phase <i>a</i> winding</li> <li>CSR input current phase reference</li> <li>CSR input voltages phase</li> <li>IMC output stage Active vector applied first in the SVM switching period</li> <li>IMC output stage Active vector applied second in the SVM switching period</li> <li>SynRM saliency ratio</li> <li>IMC output stage Null vector in the SVM switching period (DVSI group II vectors SVM strategy)</li> <li>IMC output stage Null vector applied first in the SVM switching period</li> <li>IMC output stage Null vector applied first in the SVM switching period</li> <li>IMC output stage Null vector applied first in the SVM switching period</li> <li>IMC output stage Null vector applied first in the SVM switching period</li> <li>IMC syntheside SVM strategy)</li> <li>IMC output stage Null vector applied first in the SVM switching period</li> <li>IMC output stage Null vector applied first in the SVM switching period</li> <li>IMC syntheside SVM strategy)</li> <li>IMC output stage Null vector applied second in the SVM switching period</li> <li>IMC input stage vector applied first in the SVM switching period</li> </ul> |

| $arphi_{ref}^R$                | IMC input stage reference phase for duty cycles computation  |

|--------------------------------|--------------------------------------------------------------|

| $arphi_{ref}^{I}$              | IMC output stage reference phase for duty cycles computation |

| $\psi_d, \; \psi_q, \; \psi_z$ | SynRM stator flux linkages in the dqz rotor reference frame  |

| ω <sub>e</sub>                 | SynRM electrical velocity                                    |

| $\omega_m$                     | SynRM mechanical velocity                                    |

|                                |                                                              |

#### ACRONYMS

- AC Alternated Current

- CMV Common Mode Voltage

- CSR Current Source Rectifier

- DC Direct Current

- DMC Direct Matrix Converter

- DTC Direct Torque Control

- DVSI Dual Voltage Source Inverter

- EMI Electromagnetic Interference

- EV-Electric Vehicle

- FEA Finite Element Analysis

- FOC Field Oriented Control

- FPGA Field Programmable Gate Array

- GaN Gallium Nitride

- HEMT Hight Electron Mobility Transistor

- IM Induction Machine

- IC Integrated Circuit

- IM Induction Machine

- IMC Indirect Matrix Converter

- IMD Integrated Motor Drive

- LUT Look up table

- MPC Model Predictive Controller

- MPF Maximum Power Factor

- MTPA Maximum Torque per Ampere

- MTPkVA Maximum Torque per kilo Volt-Ampere

- MTPV Maximum Torque per Volt

- $OEW-Open\text{-}End\ Winding$

- PI Proportional Integral Controller

PMSM – Permanent Magnet Synchronous Machine

PWM – Pulse Width Modulation

- RLS Recursive Least Squares

- Si-Silicon

- SiC Silicon Carbide

- SoC System on a Chip

- SVM Space Vector Modulation

- SynRM Synchronous Reluctance Machine

- THD Total Harmonic Distortion

- VSD Variable Speed Drive

- VSI Voltage Source Inverter

- WBG Wide-bandgap

- ZSC Zero sequence currents

## TABLE OF CONTENTS

| CHAPTER 1                                                         | 1  |

|-------------------------------------------------------------------|----|

| Introduction                                                      | 1  |

| 1.1 – Research Background                                         | 1  |

| 1.2 – Motivation                                                  | 15 |

| 1.3 – Thesis Objectives and Contributions                         | 16 |

| 1.4 – Contributions                                               | 17 |

| 1.5 – Thesis Outline                                              | 18 |

| CHAPTER 2                                                         | 19 |

| Indirect Matrix Converter with a DVSI Output                      | 19 |

| 2.1 – Common Mode Voltage Computation                             |    |

| 2.2 – Input Stage (Current Source Rectifier)                      |    |

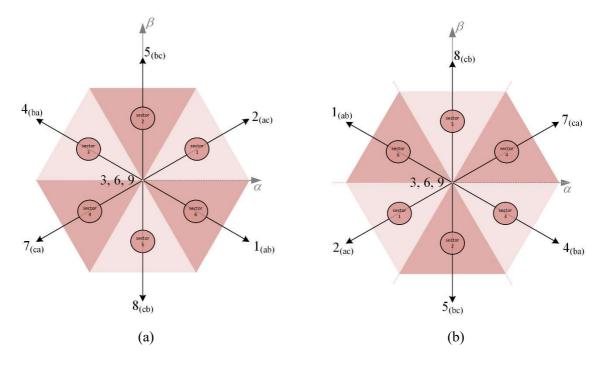

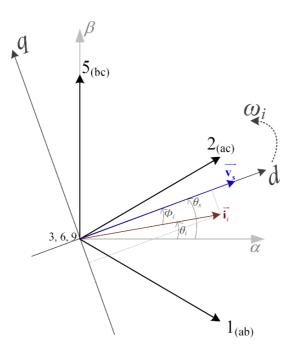

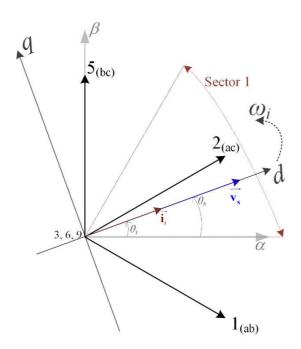

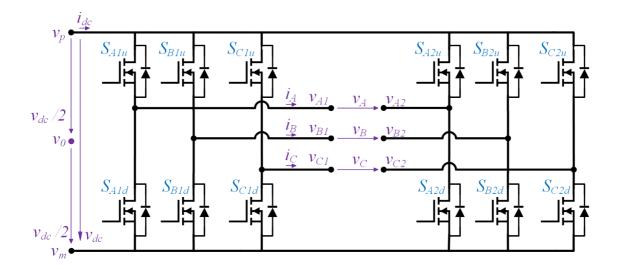

| 2.3 – Output Stage (Dual Voltage Source Inverter)                 |    |

| 2.4 – Association of the CSR and DVSI                             | 47 |

| 2.5 – Analysis of OEW IMC SVM Methods                             |    |

| CHAPTER 3                                                         | 65 |

| Synchronous Reluctance Machine                                    | 65 |

| 3.1 – SynRM Mathematical Model                                    |    |

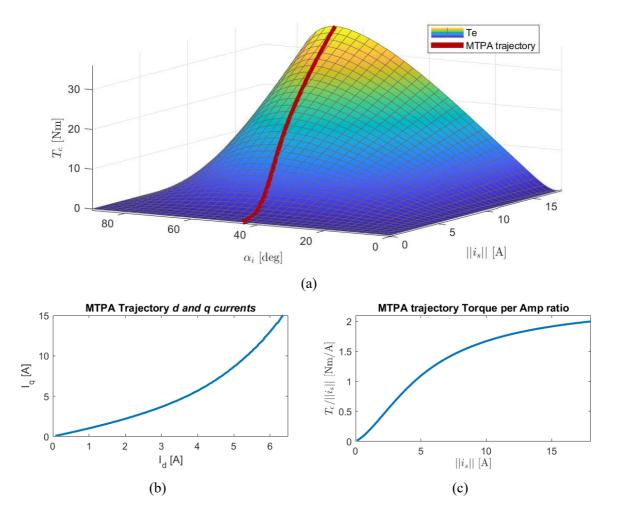

| 3.2 – SynRM Operating Trajectories                                | 70 |

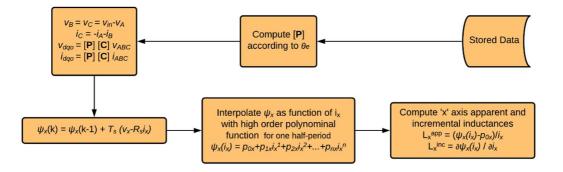

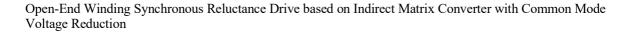

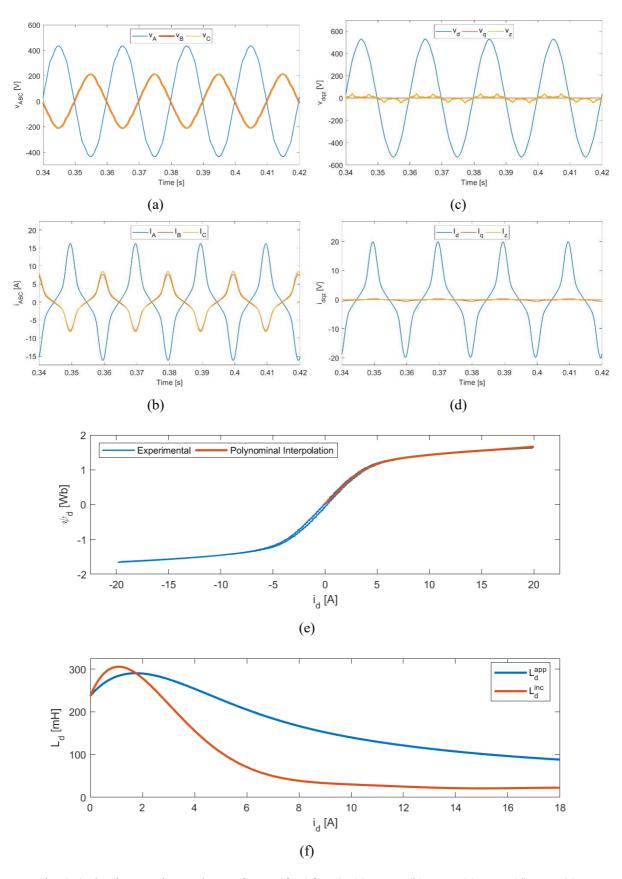

| 3.3 – SynRM Parameter Identification                              | 72 |

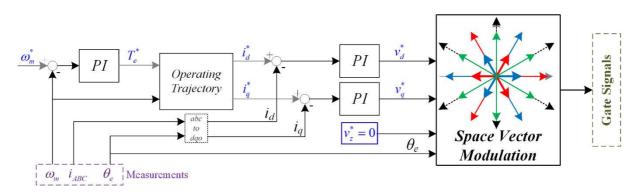

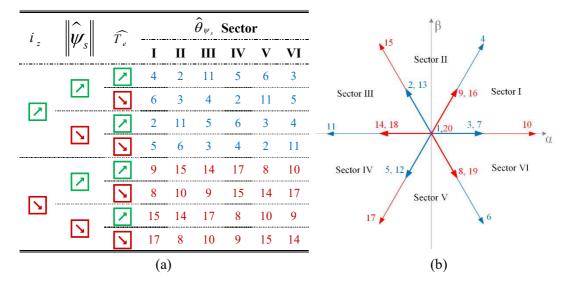

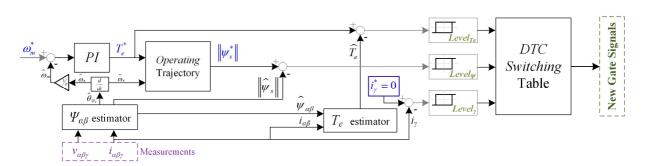

| 3.4 – SynRM Control strategies                                    | 78 |

| CHAPTER 4                                                         | 83 |

| OEW SynRM Drive based on IMC with CMV reduction                   | 83 |

| 4.1 – Adaptive non-linear Backstepping Speed controller for SynRM |    |

| 4.2 – Novel SVM strategy for CMV reduction                        | 91 |

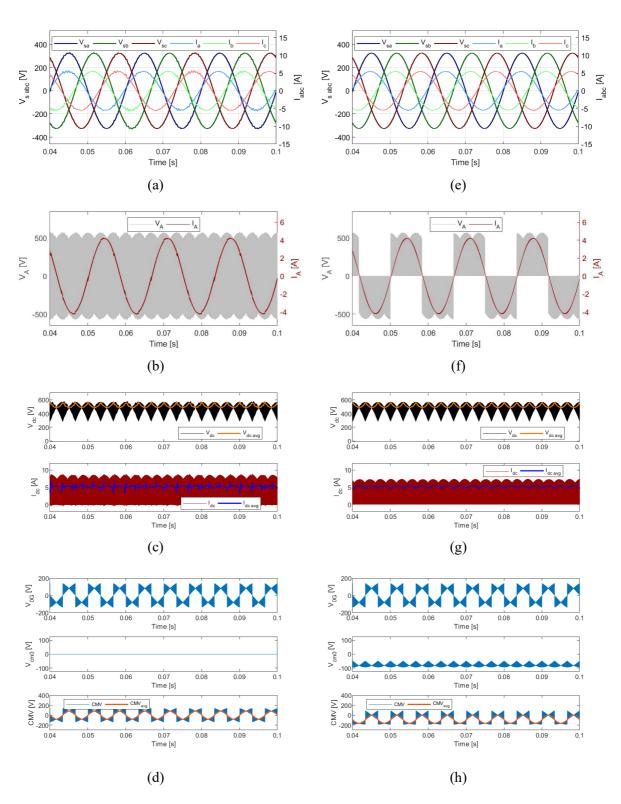

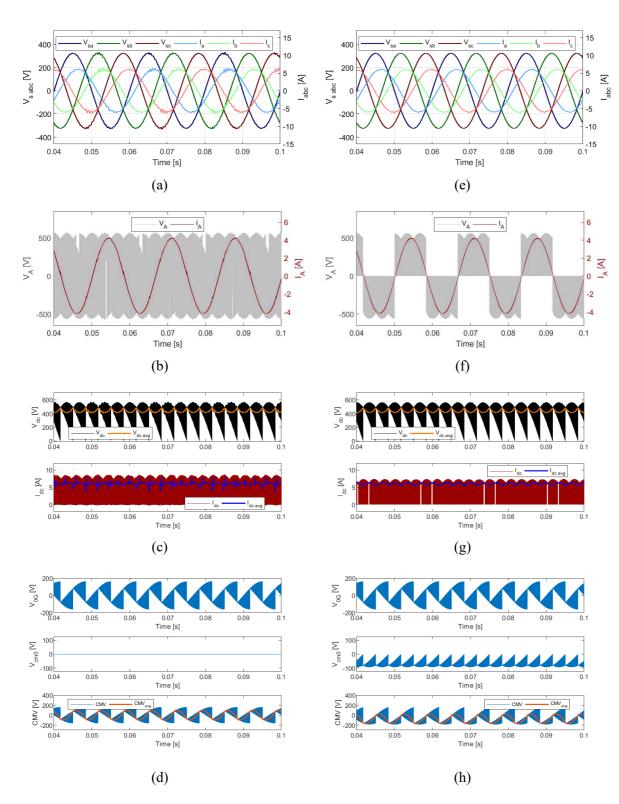

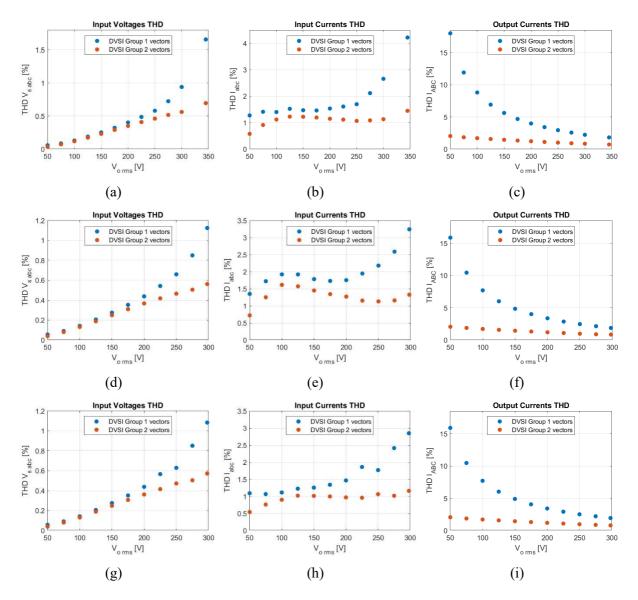

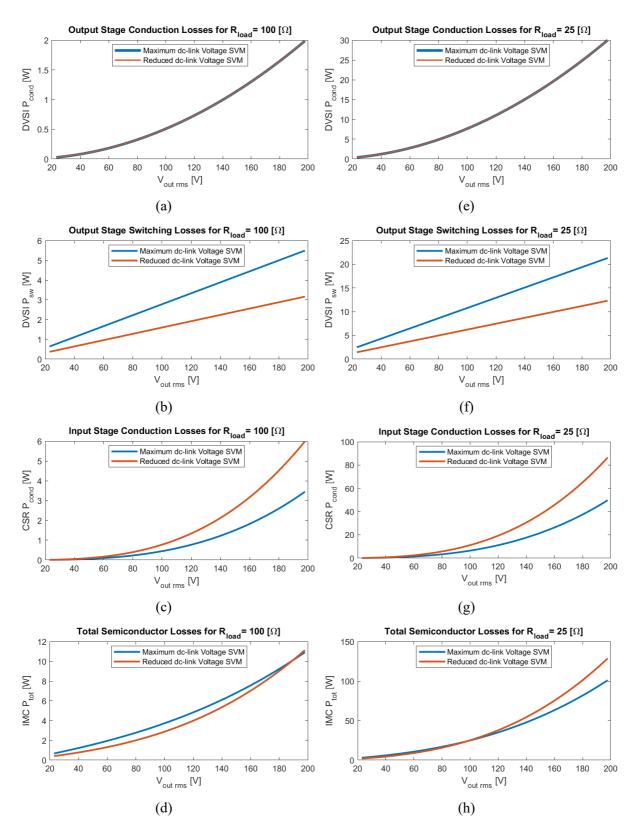

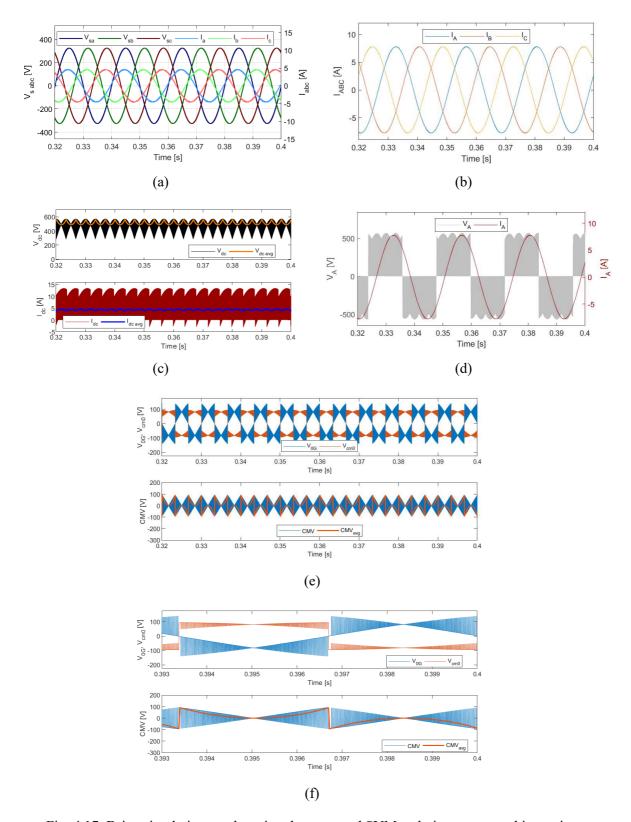

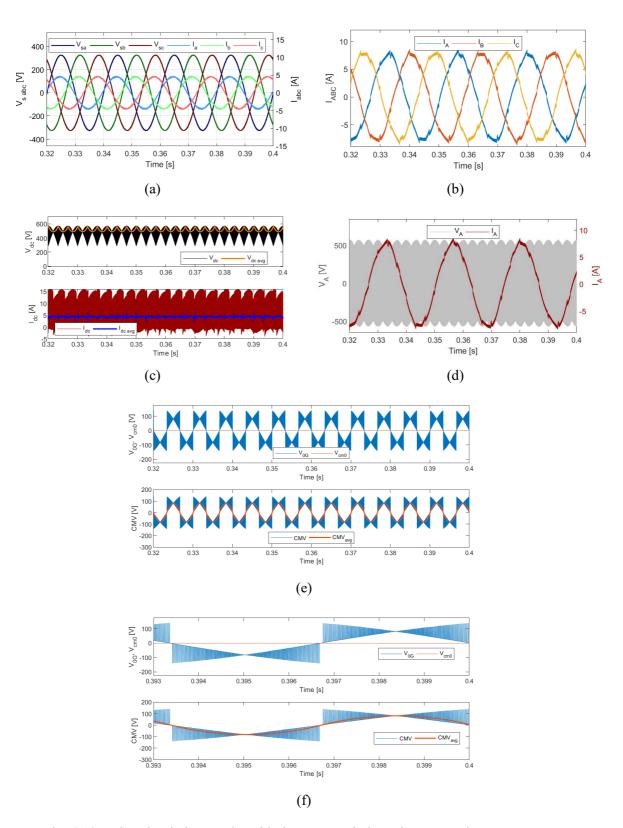

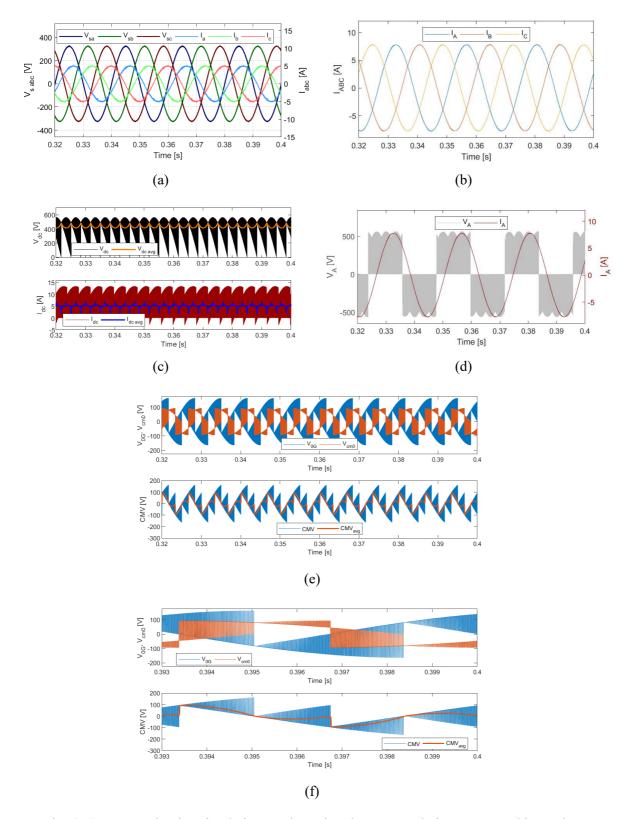

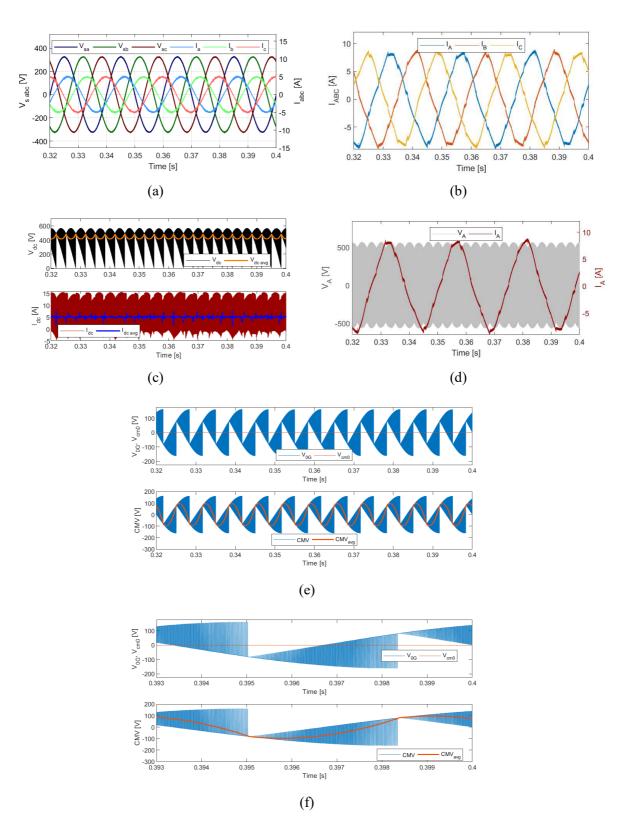

| 4.3 –     | Simulation Results                                          |     |

|-----------|-------------------------------------------------------------|-----|

| СНАРТИ    | ER 5                                                        | 121 |

| Experime  | ental Validation                                            |     |

| 5.1 –     | Laboratorial Prototype Implementation                       |     |

| 5.2 –     | Adaptive non-linear Backstepping Speed controller for SynRM |     |

| 5.3 –     | Novel SVM strategy for CMV reduction                        |     |

| 5.4 –     | Experimental Work Conclusions                               |     |

| СНАРТИ    | ER 6                                                        | 147 |

| Conclusi  | ons                                                         |     |

| 6.1 –     | Final Considerations                                        |     |

| 6.2 –     | Future Work                                                 |     |

| Bibliogra | nphy                                                        |     |

| APPEND    | DIX A                                                       | 161 |

| Tradition | nal FOC Gains Computation                                   |     |

| APPEND    | DIX B                                                       | 169 |

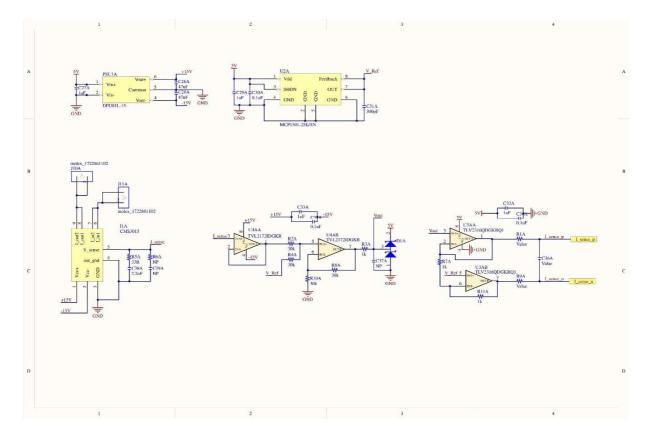

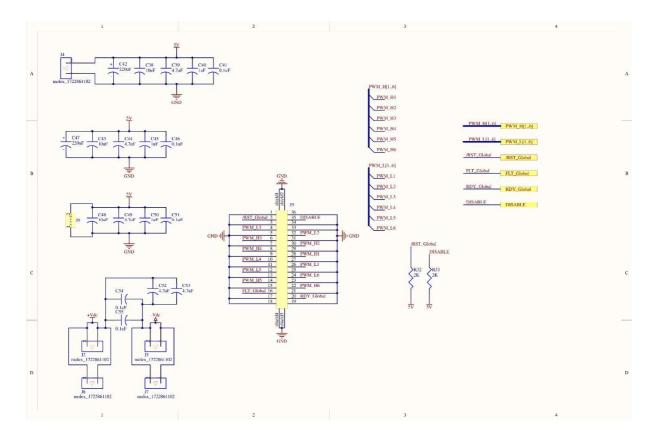

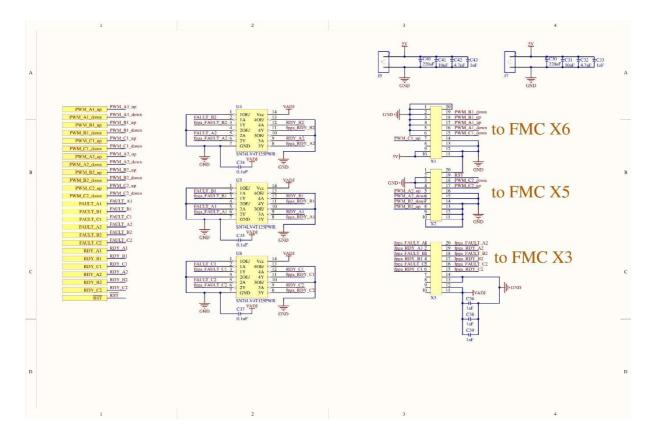

| Signal Ad | cquisition Board                                            |     |

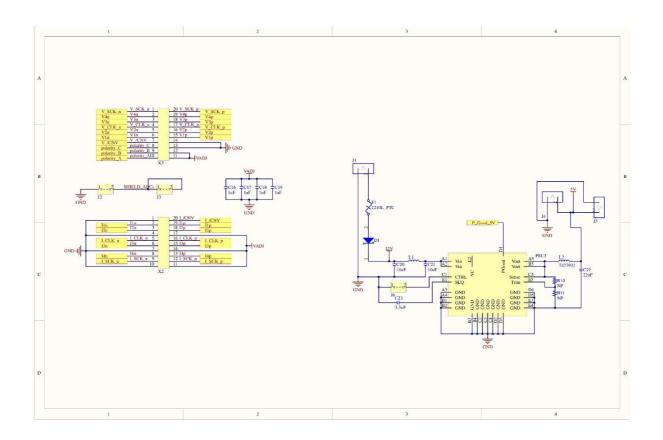

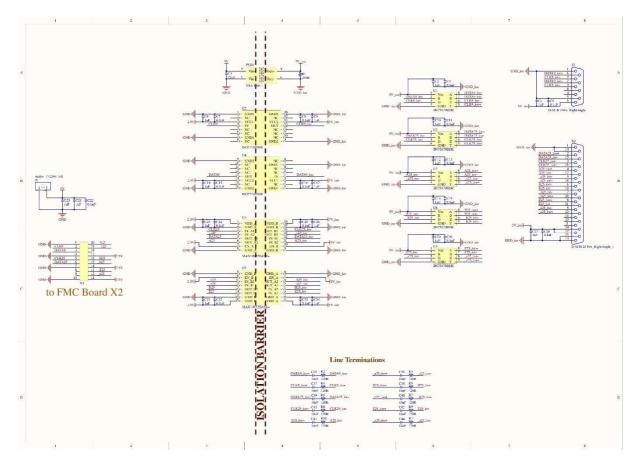

| B1.       | Top Schematic                                               |     |

| B2.       | Current Sensing Schematic                                   |     |

| В3.       | Voltage Sensing Schematic                                   |     |

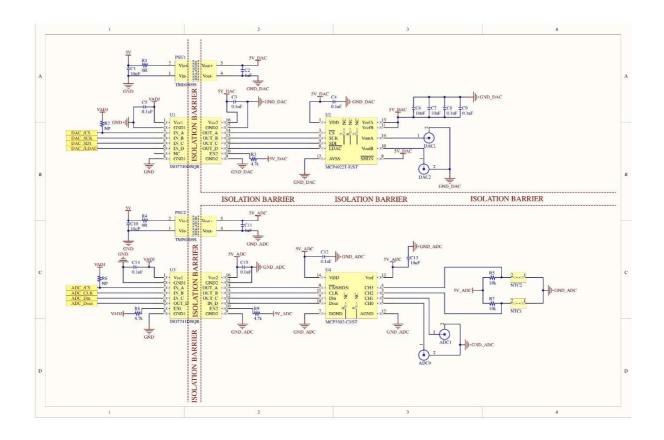

| B4.       | Analog to Digital Converters                                |     |

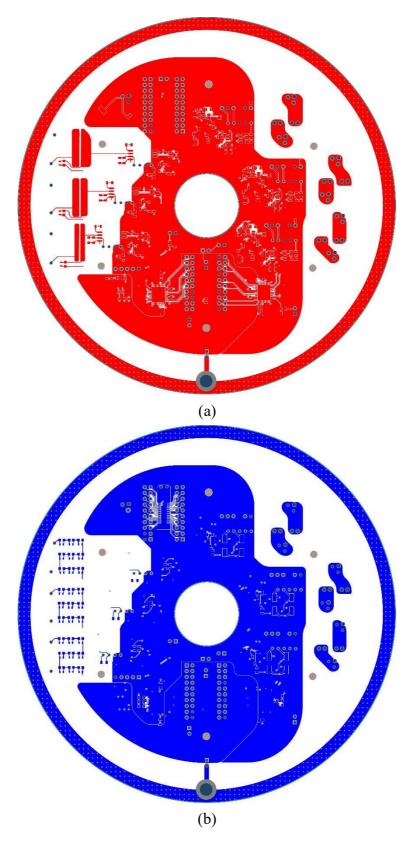

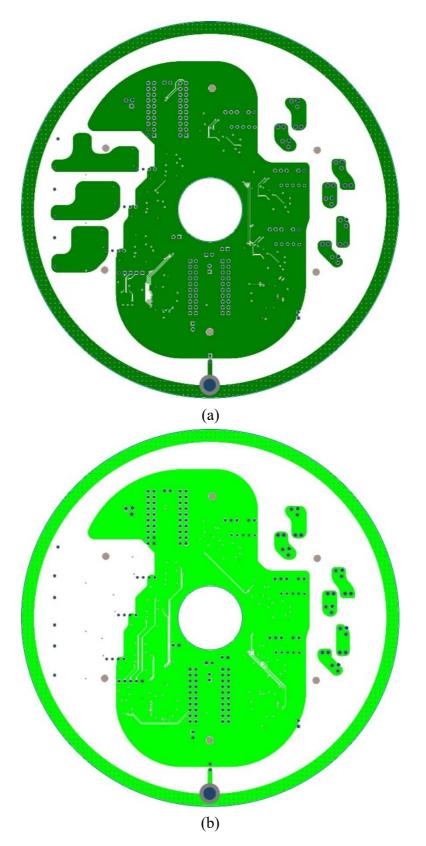

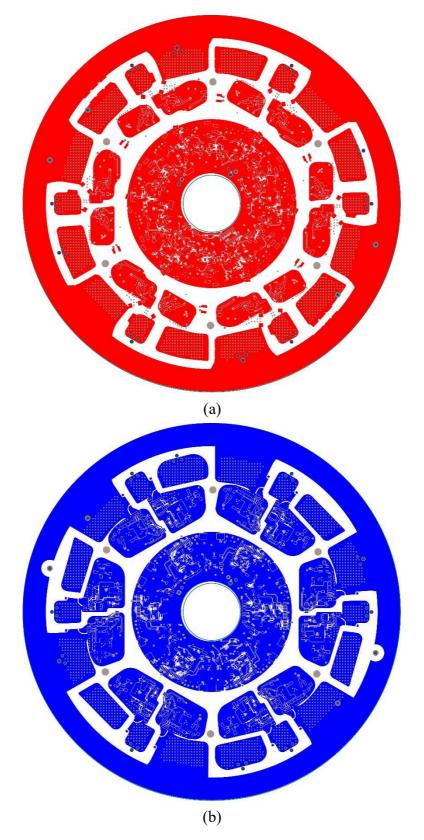

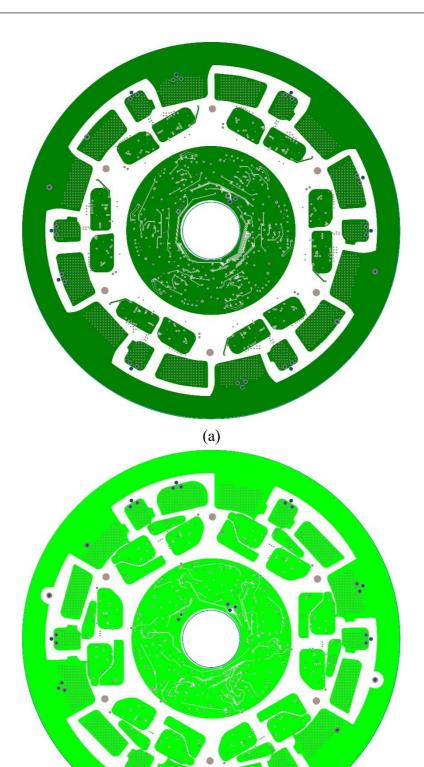

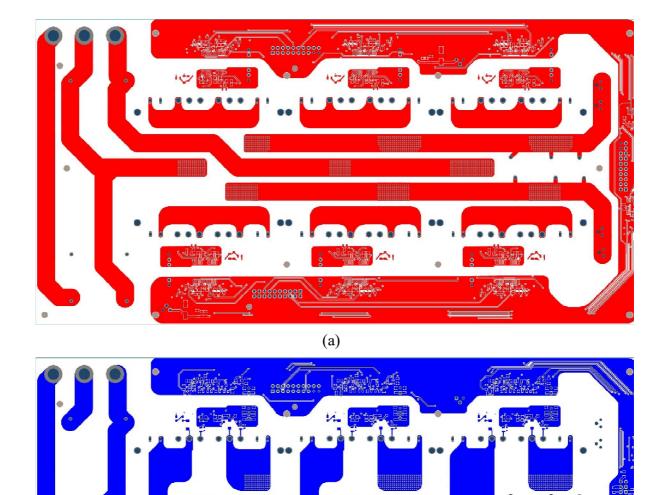

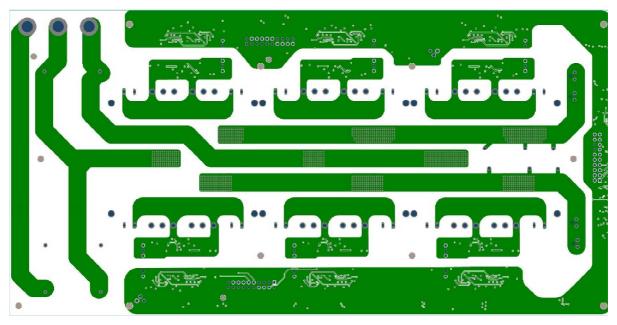

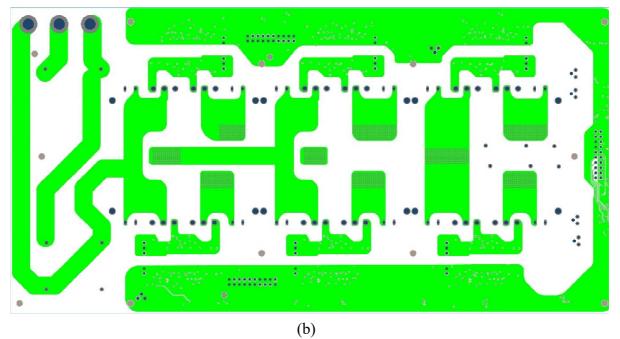

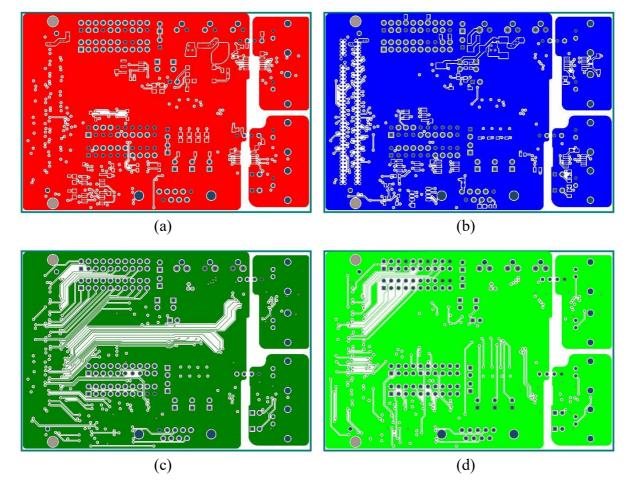

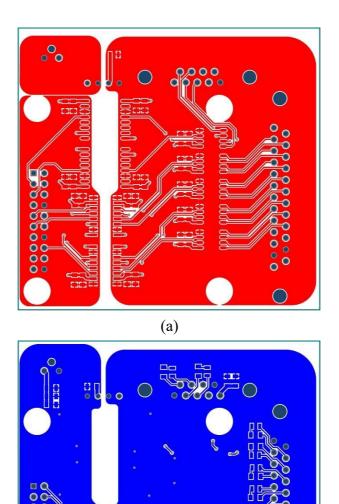

| В5.       | Printed Circuit Board Copper Layers                         |     |

| APPEND    | DIX C                                                       | 175 |

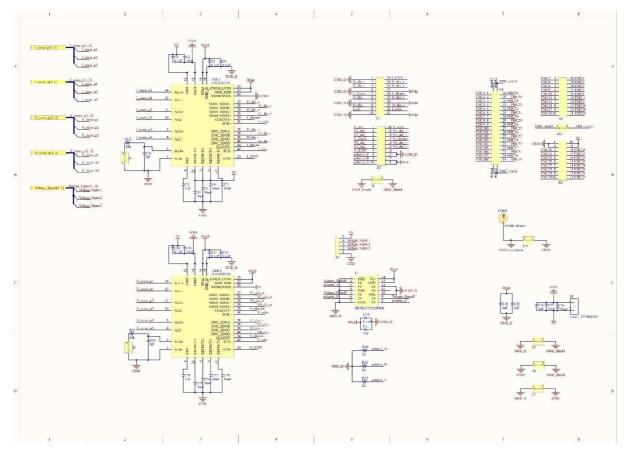

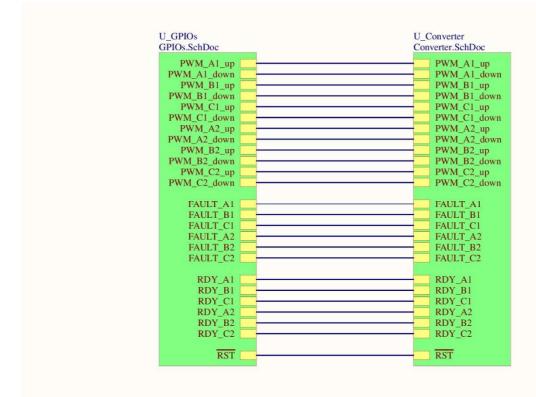

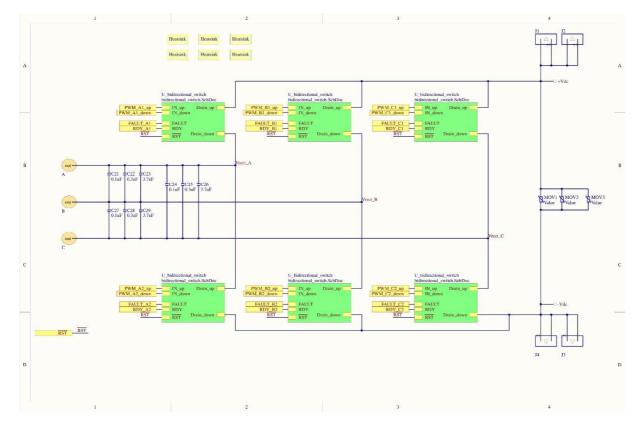

| Dual Vol  | tage Source Inverter Board                                  |     |

| C1.       | Top Schematic                                               |     |

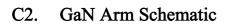

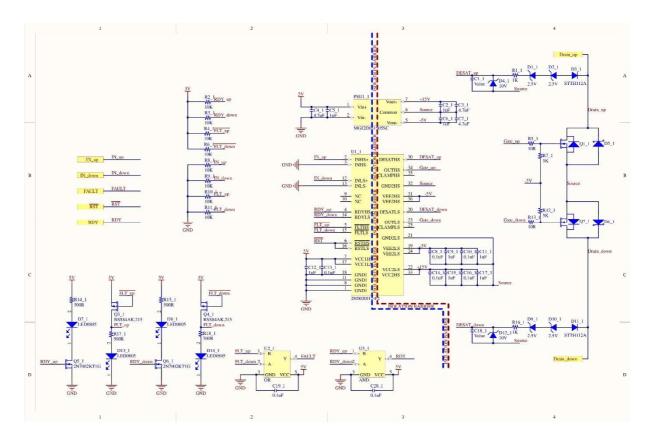

| C2.       | GaN Arm Schematic                                           |     |

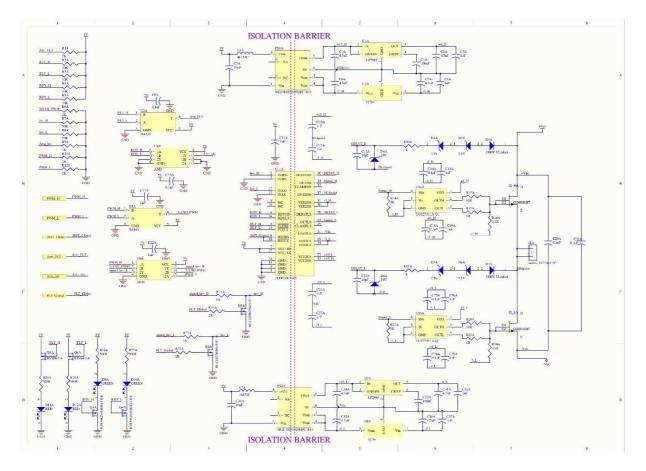

| C3.       | Aggregation of Driver Signals Schematic          | . 177 |

|-----------|--------------------------------------------------|-------|

| C4.       | I/O Schematic                                    | . 178 |

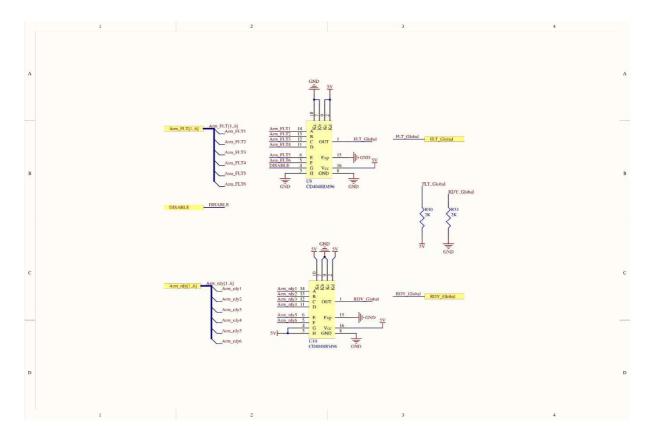

| C5.       | Printed Circuit Board Copper Layers              | . 179 |

| APPEND    | IX D                                             | 181   |

| Current S | ource Rectifier Board                            | . 181 |

| D1.       | Top Schematic                                    | . 181 |

| D2.       | Current Source Rectifier Schematic               | . 182 |

| D3.       | Bidirectional Switch Schematic                   | . 183 |

| D4.       | I/O Schematic                                    | . 184 |

| D5.       | Printed Circuit Board Copper Layers              | . 185 |

| APPEND    | IX E                                             | 187   |

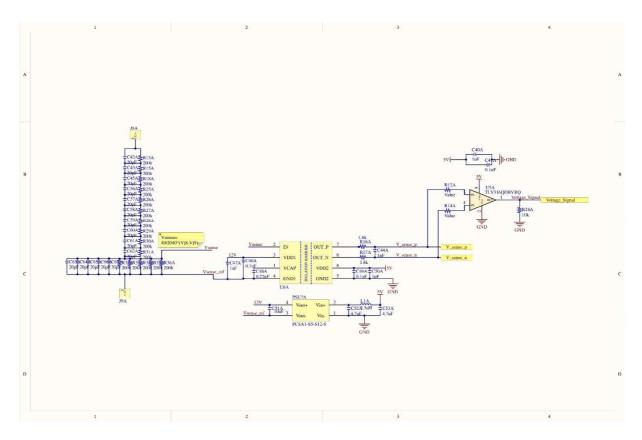

| FMC Boa   | rd                                               | . 187 |

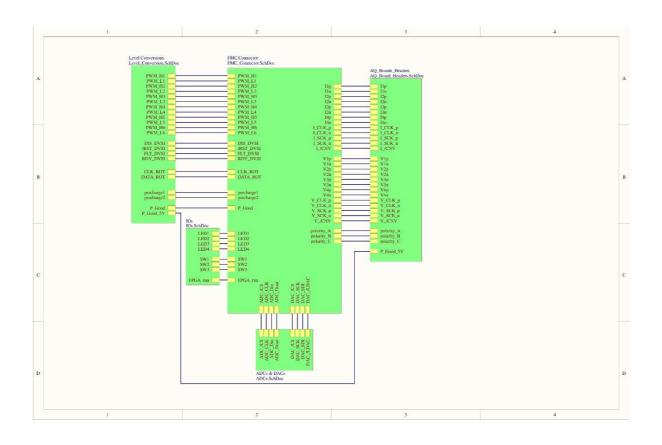

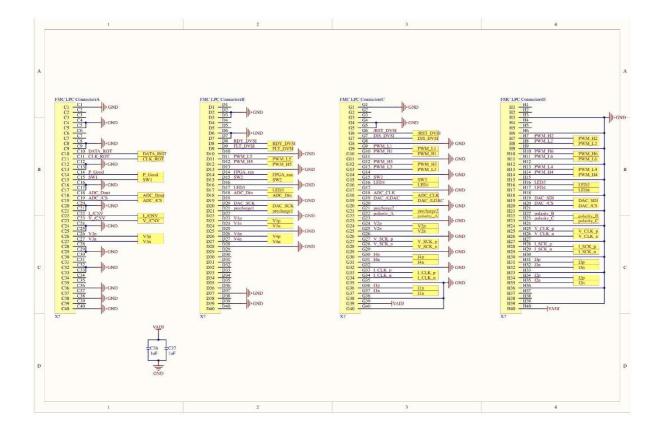

| E1.       | Top Schematic                                    | . 187 |

| E2.       | FMC Connector Schematic                          | . 188 |

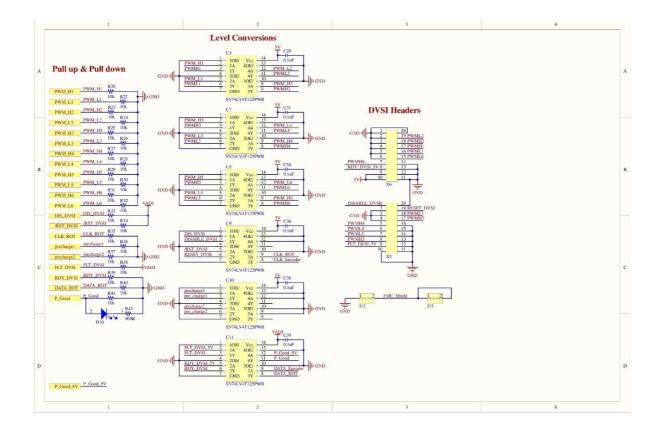

| E3.       | Power Supply and Acquisition Board I/O Schematic | . 189 |

| E4.       | Level Conversion and DVSI I/O Schematic          | . 190 |

| E5.       | ADCs and DACs Schematic                          | . 191 |

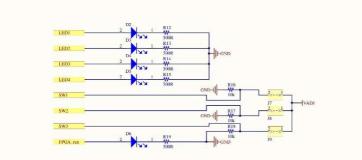

| E6.       | LEDs and Switches for User Interface Schematic   | . 191 |

| E7.       | Printed Circuit Board Copper Layers              | . 192 |

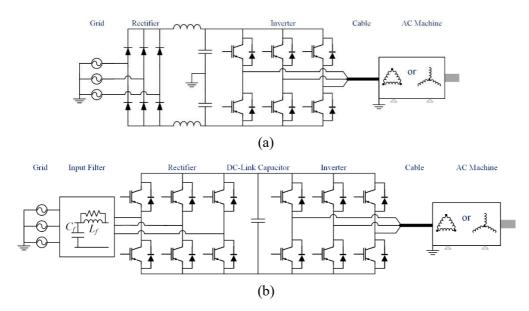

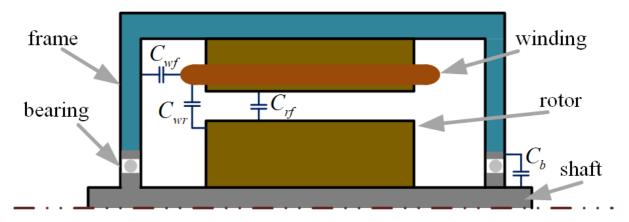

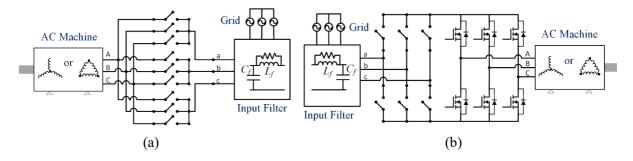

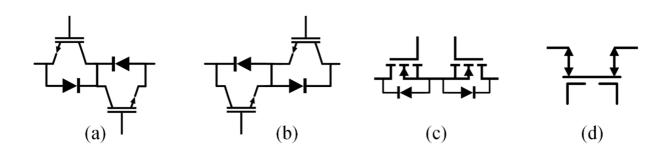

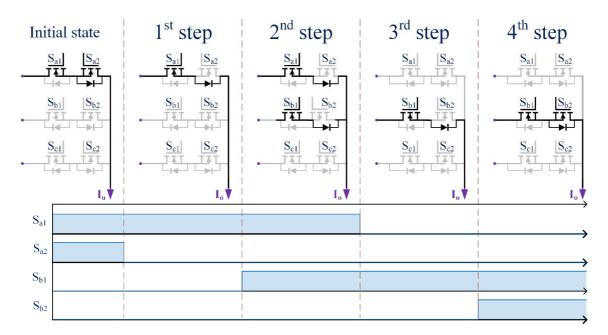

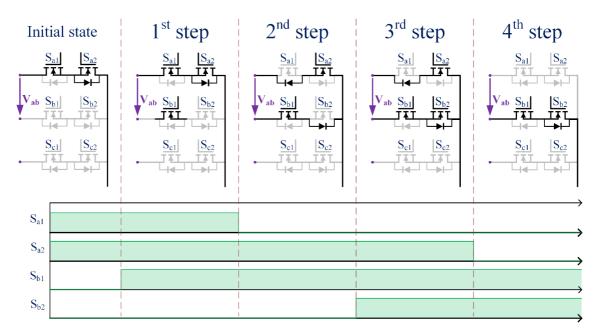

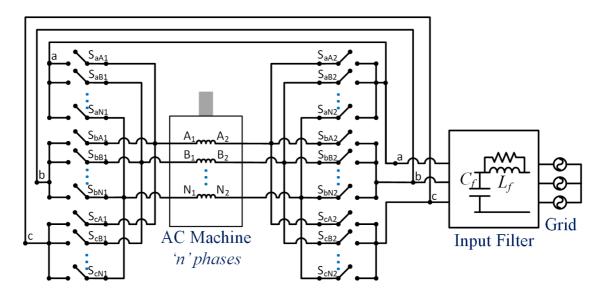

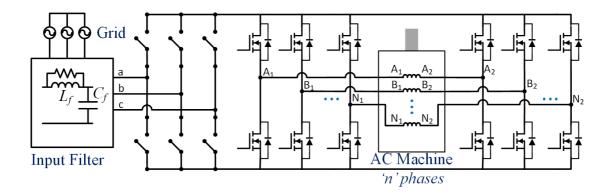

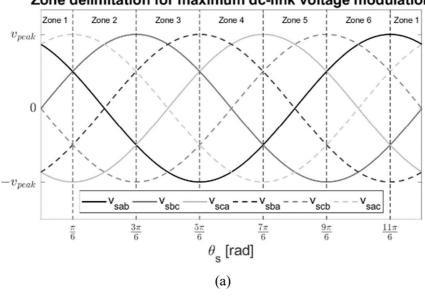

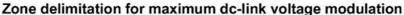

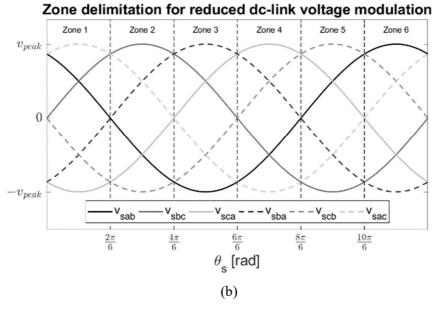

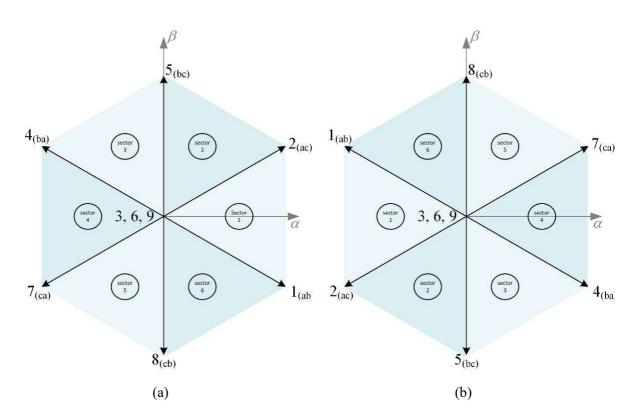

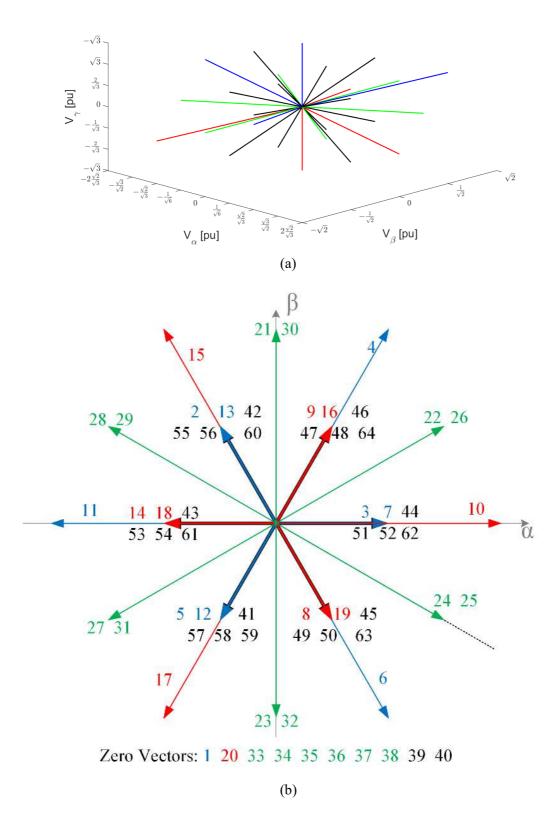

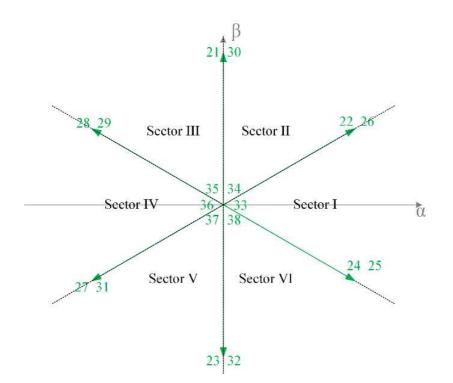

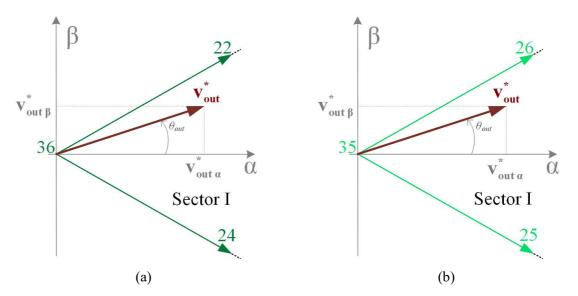

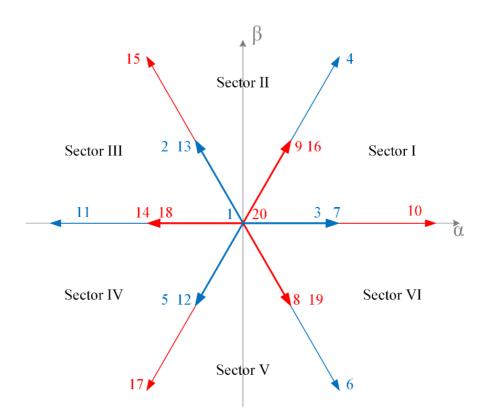

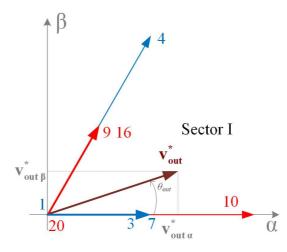

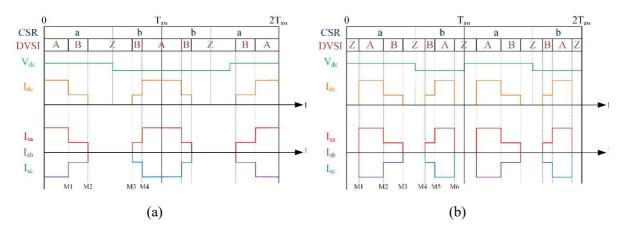

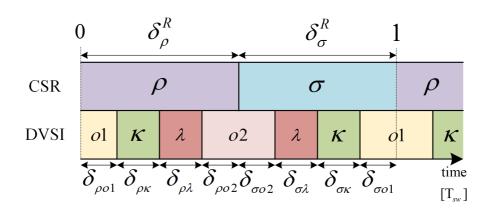

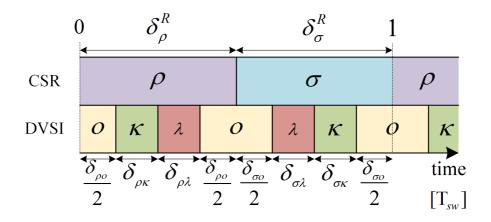

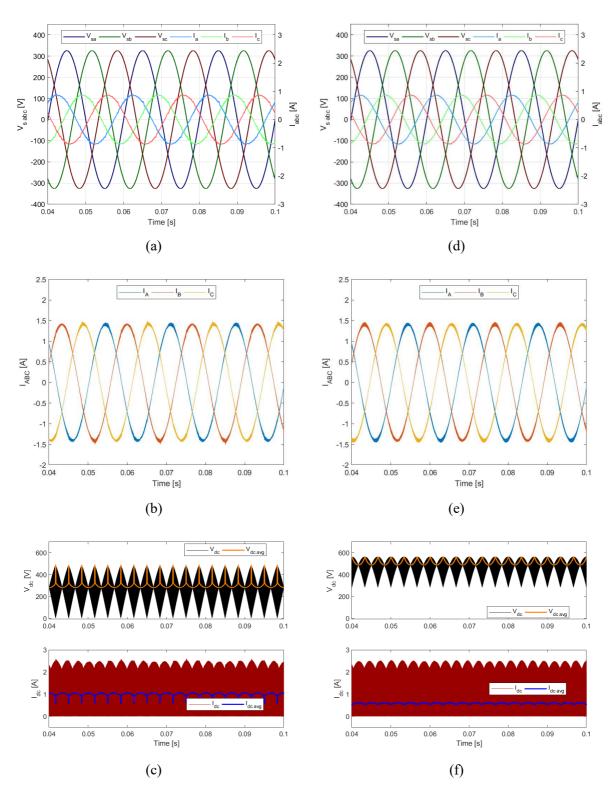

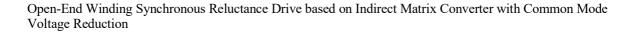

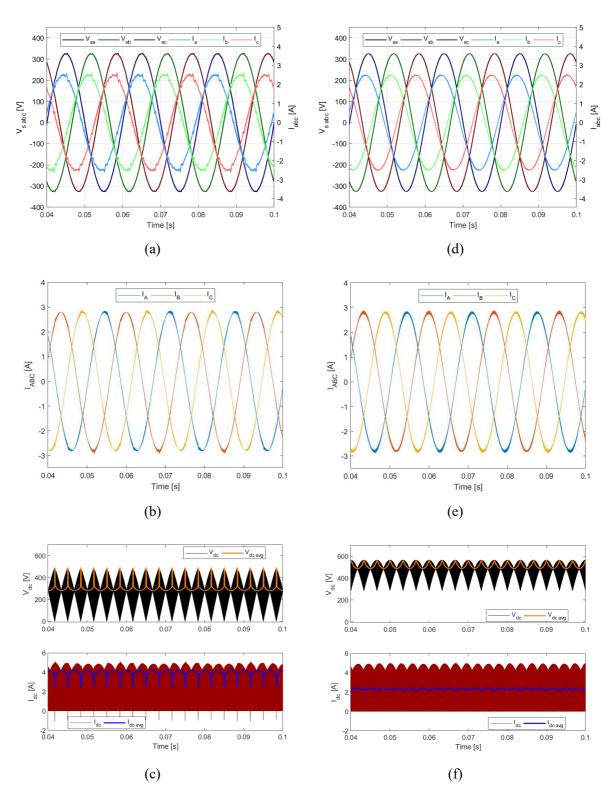

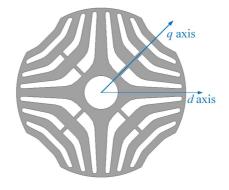

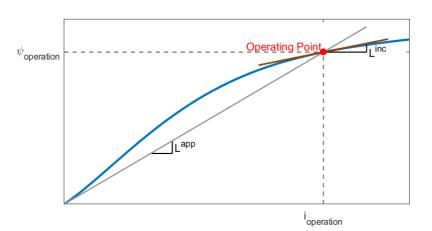

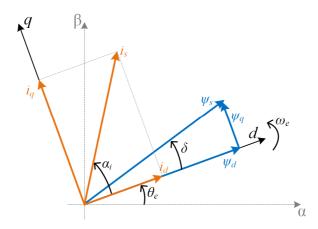

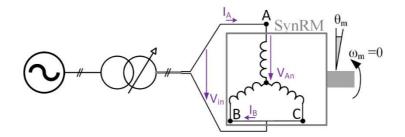

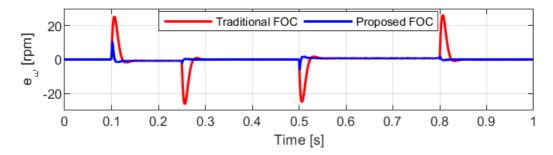

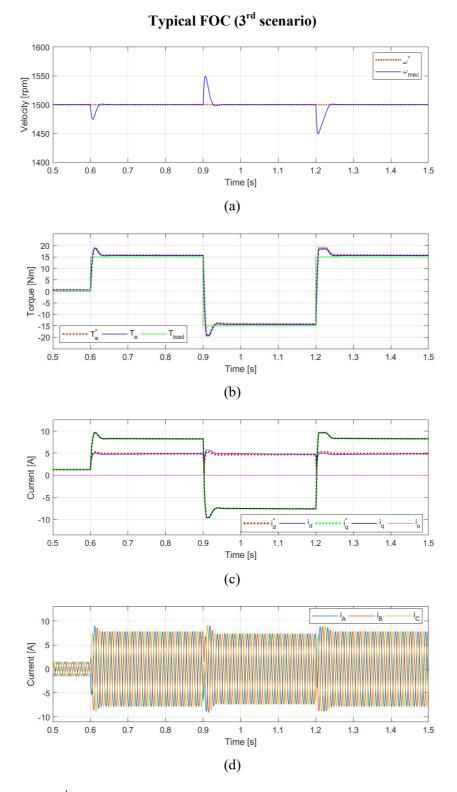

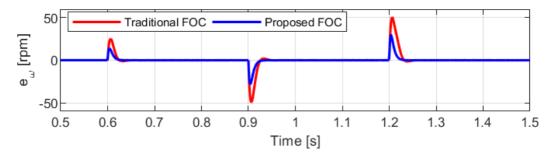

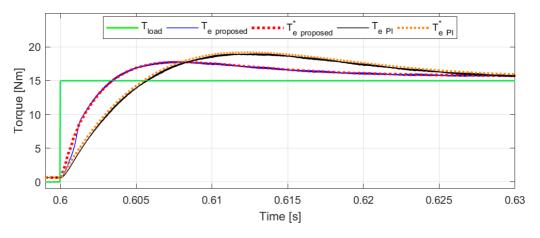

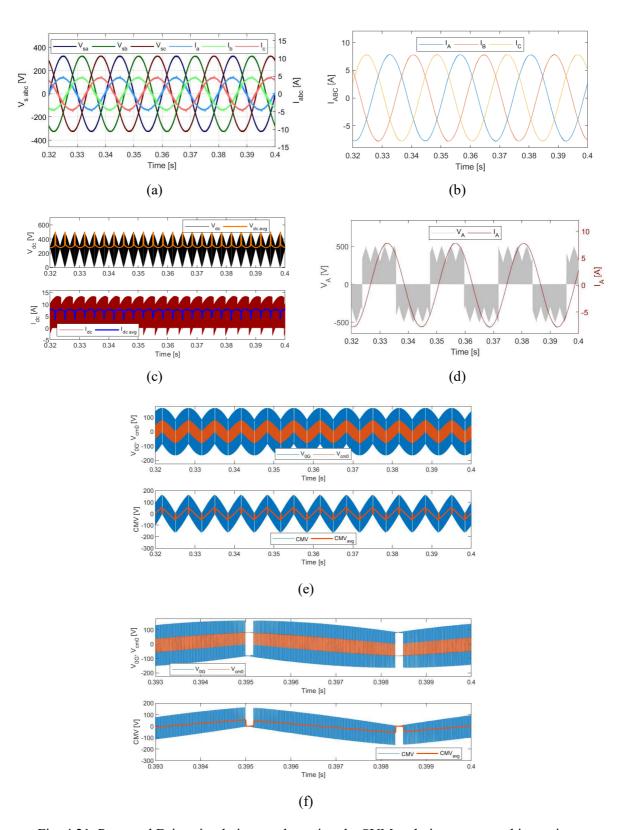

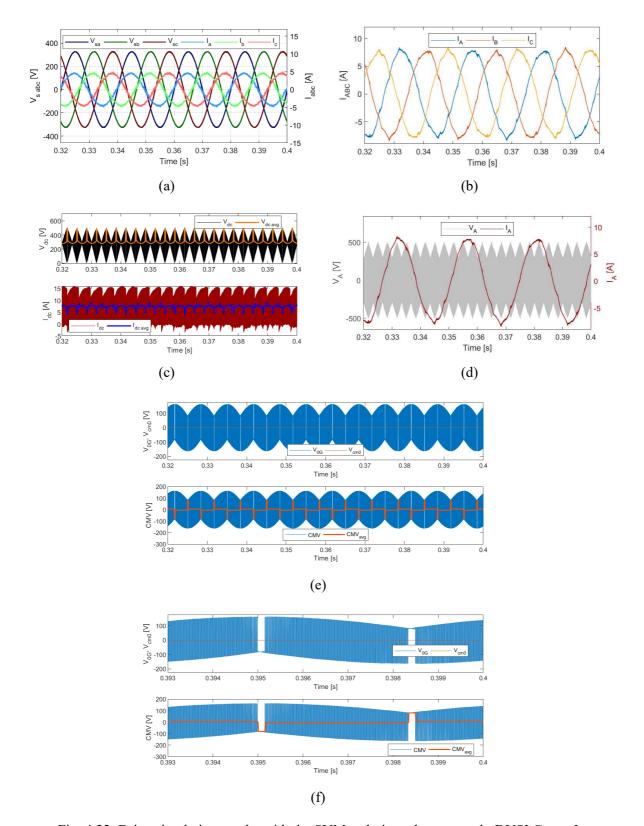

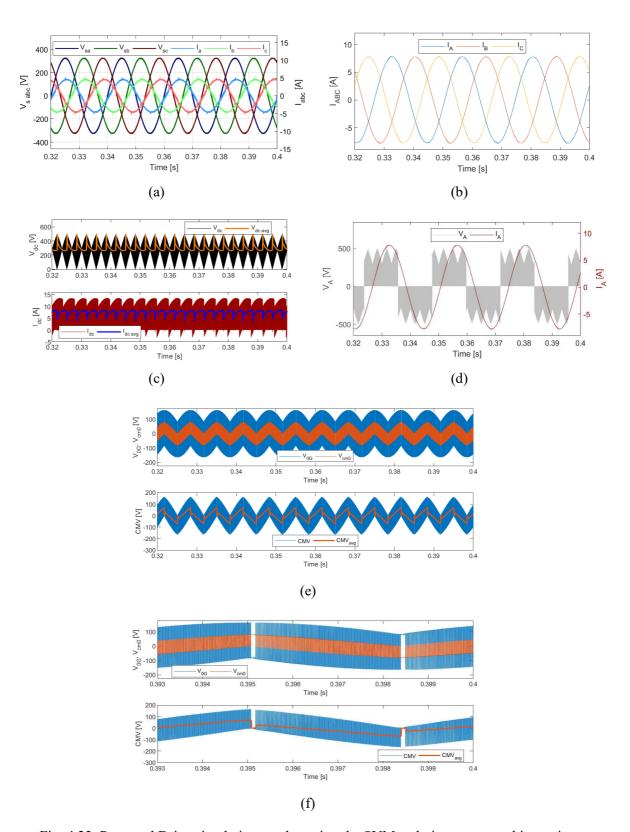

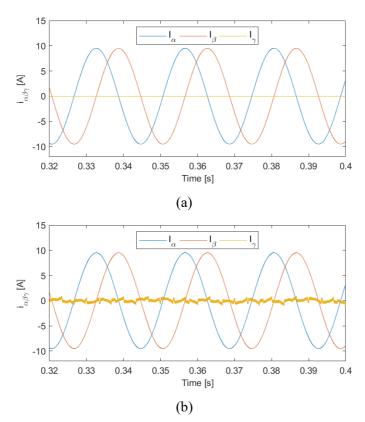

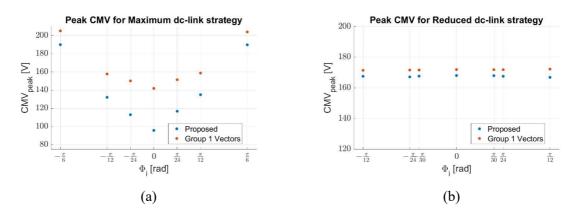

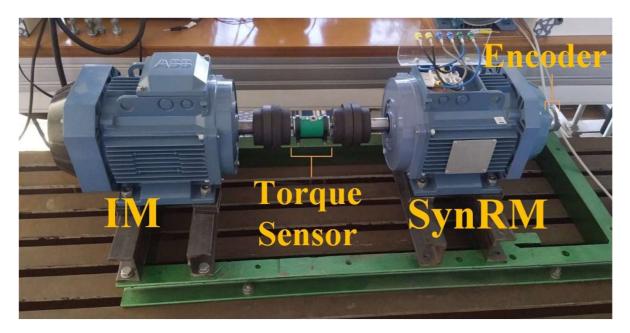

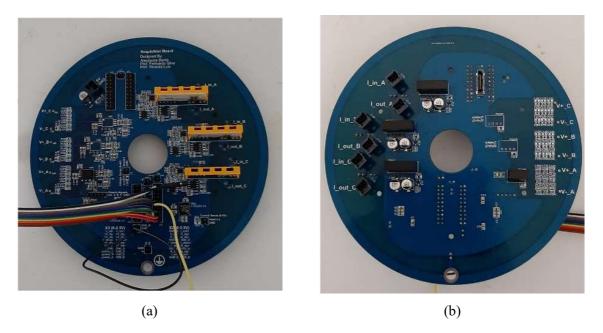

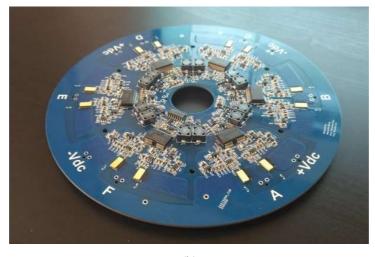

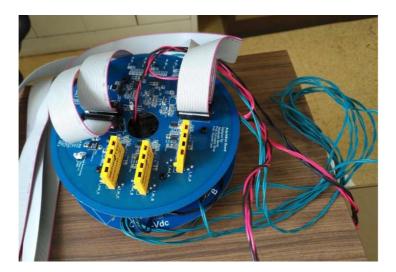

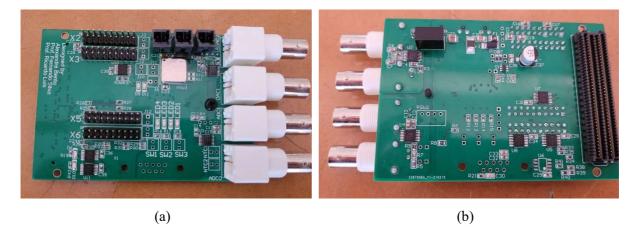

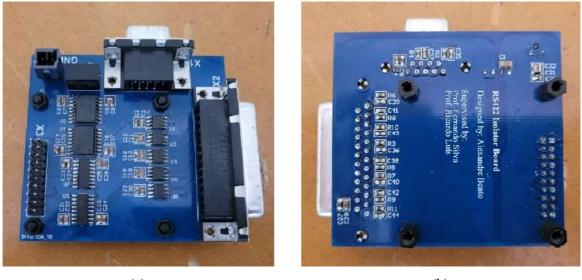

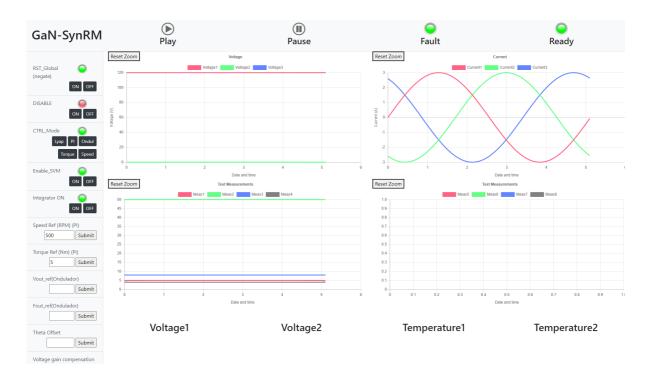

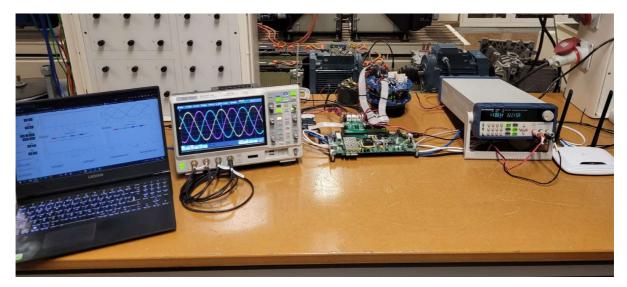

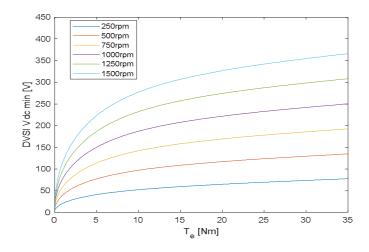

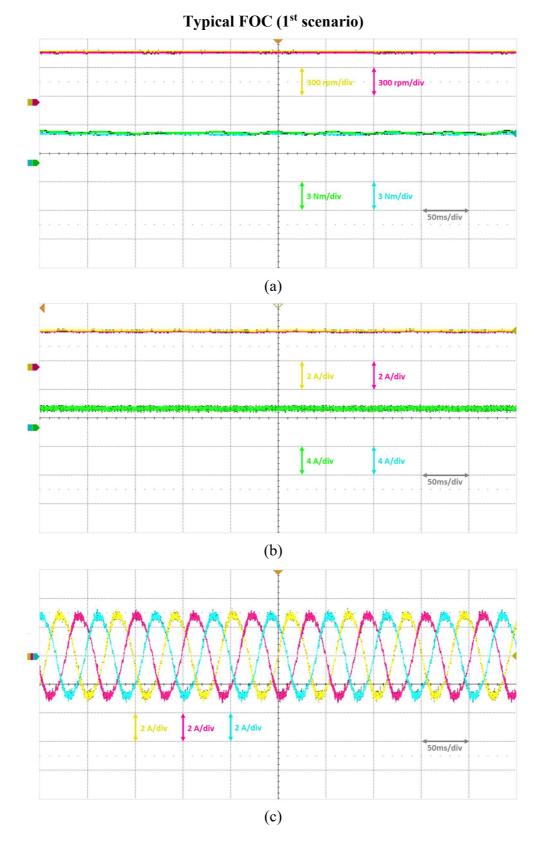

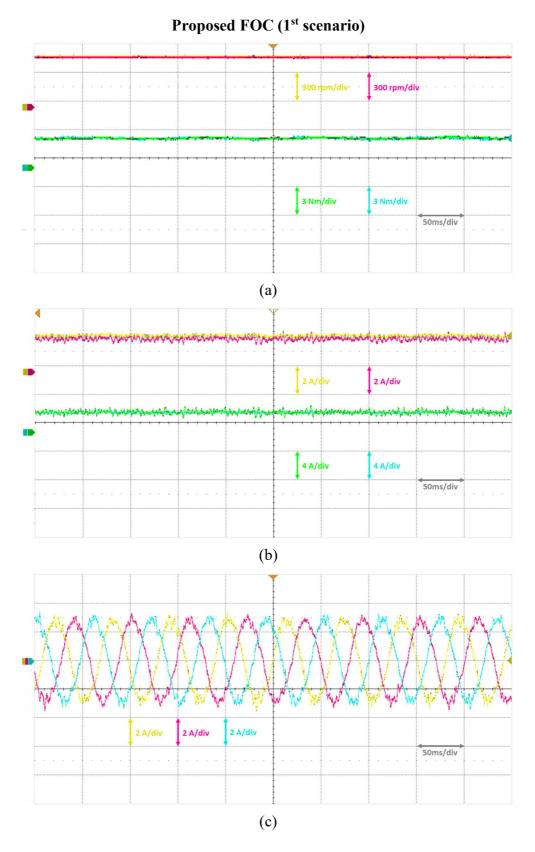

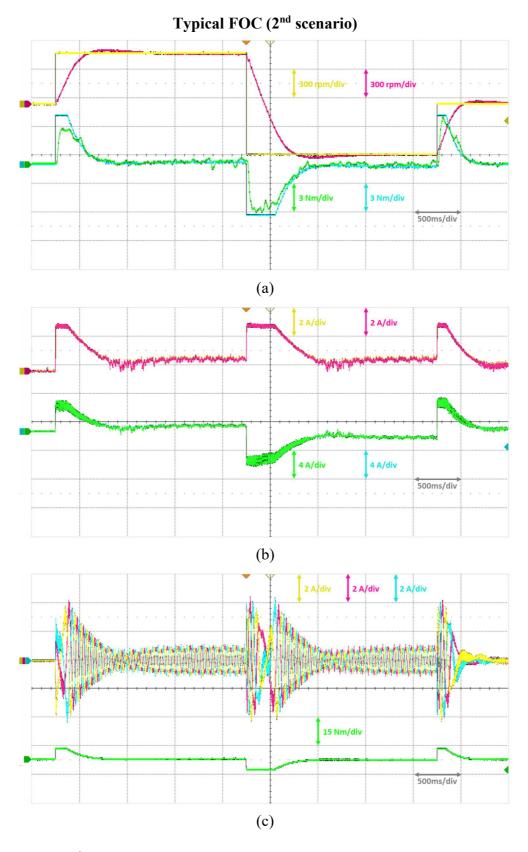

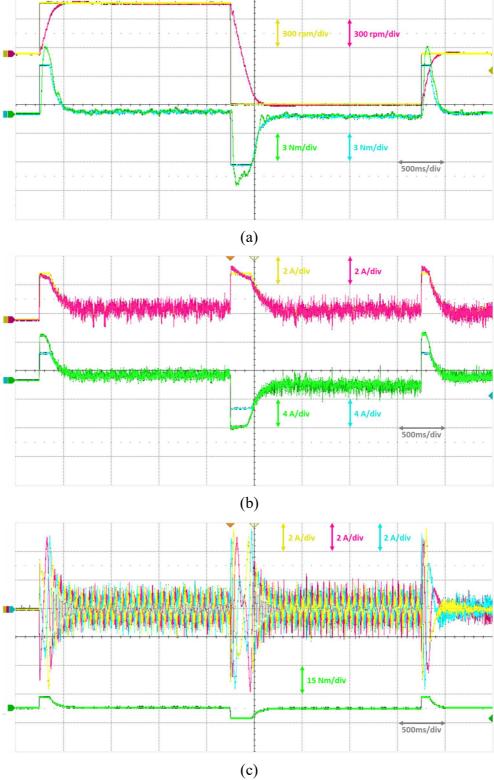

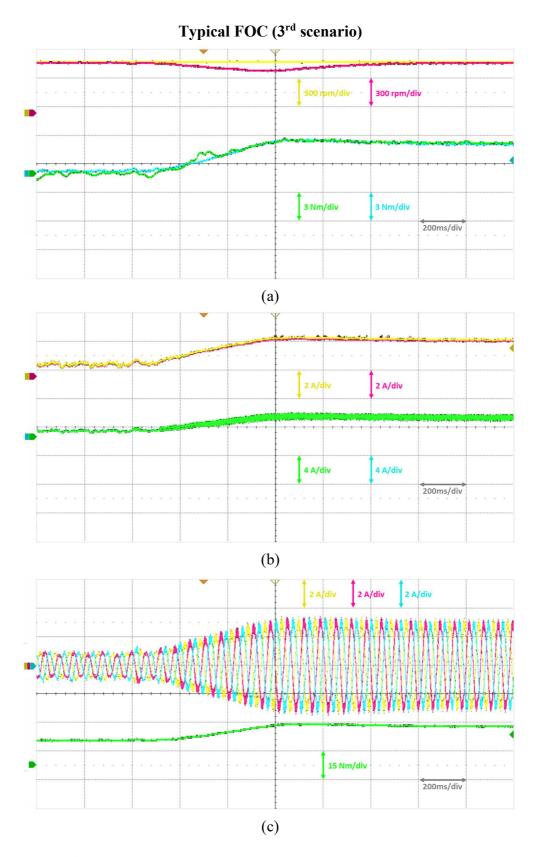

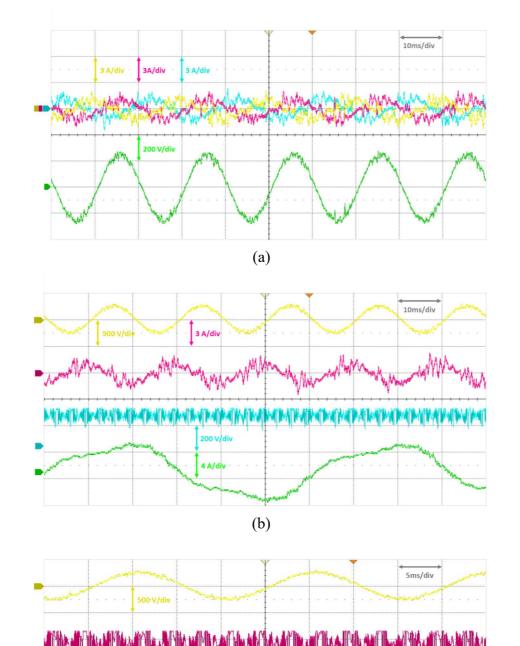

| APPEND    | IX F                                             | 193   |