## Universal Verification Methodology for Power Management Unit

### Márcio Éder Sequeira Soares

Thesis to obtain the Master of Science Degree in

## **Electrical and Computer Engineering**

Supervisors: Prof. Marcelino Bicho dos Santos Prof. Jorge Manuel Dos Santos Ribeiro Fernandes

#### **Examination Committee**

Chairperson: Prof. Teresa Maria Canavarro Menéres Mendes de Almeida Supervisor: Prof. Marcelino Bicho dos Santos

Member of the Committee: Prof. Fernando Manuel Duarte Gonçalves

## **Declaration**

I declare that this document is an original work of my own authorship and that it fulfills all the requirements of the Code of Conduct and Good Practices of the Universidade de Lisboa.

To my parents...

## **Acknowledgments**

First of all I would like to thank my supervisors Professor Marcelino Bicho dos Santos and Jorge Fernandes for their counselling and support but also for their availability during this dissertation.

This work is dedicated to my parents, Valdemar da Cruz Soares and Marcelina do Rosário Sequeira. Everything I've ever accomplished in my life is because of them. Their unconditional love, their guidance, sacrifice and commitment to family made me into the person I am today. I want to thank my brother and sister, Odracir Almeida and Maura Soares for their love and for always checking up on me during good and bad times. Thank you Irineu Justino Delgado, Anabela de Melo, Alberto Monteiro, Eunice Matos and Gustavo Almeida for embracing me throughout all these years.

I would like to thank all the people at SiliconGate for all the teachings and all the shared moments. To João Lucas Munhão, thank you for everything. I cannot express how deeply thankful I am for everything he's done for me. I thank him for his patience, for all the teachings, and above it all for being my friend. A special thank you for Tiago Moita, André Agostinho, Válter Sádio and Bruno Santos.

To all my friends, thank you for always making me feel at home. I wish a special thank you to Carlos Santos for being by my side throughout my journey at Instituto Superior Técnico. His confidence and commitment served as example and made me work hard every single day.

And last but certainly not least, to Dânia dos Reis, thank you for always being by my side and for always pushing me to be the best version of myself. Thank you for all the love, all the advice, all the comforting and, above it all, thank you for being my partner.

This work was supported by national funds through FCT, Fundação para a Ciência e a Tecnologia, under project UIDB/50021/2020 and pAvIs, PENTA Project n. 20016.

## Resumo

Atualmente, circuitos de sinais mistos existem em larga escala na indústria dos semicondutores. Validação de circuitos de sinais mistos introduz complexidade no processo de verificação, dificultando a validação funcional. A *Universal Verification Methodology* (UVM) representa a metodologia padrão para verificação de circuitos digitais e de sinais mistos. *Real Number Modelling* permite a descrição de circuitos mistos através duma linguagem de alto nível. Esta abordagem introduz limitações no processo de verificação mas constrói alicerces para a verificação orientada a cobertura e verificação funcional. A *Universal Verification Methodology* aplicada a circuitos baseados em *Real Number Modelling* potencia a criação de ambientes de verificação robustos diminuindo significativamente o tempo de simulação, antecipando a introdução no mercado. Neste trabalho, propõe-se a implementação de um ambiente UVM para teste e verificação de reguladores de tensão e uma unidade de gestão de energia no âmbito do projeto pAvIs. Este novo método de verificação é então integrado no processo de design e teste da SiliconGate.

### **Palavras Chave**

*Universal Verification Methodology*, Unidade de Gestão de Energia, Verificação orientada a cobertura, teste de circuitos de sinais mistos, reguladores de tensão

## **Abstract**

Nowadays, mixed signal applications are widespread in the semiconductor industry. Mixed signal validation adds complexity to the verification process, which difficults functional verification Universal Verification Methodology (UVM) is the current standard methodology for verifying digital and mixed-signal designs. Real Number Modelling allows the description of mixed-signal designs using a High-level verification language. This approach imposes limitations upon the verification process but builds the foundation for coverage-driven verification and functional verification. Universal Verification Methodology applied to models based on Real Number Modelling allows for robust verification environments while significantly reducing simulation time and time-to-market. In this work, a UVM testbench environment is proposed for voltage regulators and a power management unit verification, under the scope of pAvIs project. This new verification solution is integrated in the design and test flow of SiliconGate.

## Keywords

Universal Verification Methodology, Power Management Unit, Coverage-driven Verification, mixed-signal testing, voltage regulators

## **Contents**

| 1 | Intro | oduction                                              | 1  |

|---|-------|-------------------------------------------------------|----|

|   | 1.1   | Motivation                                            | 3  |

|   | 1.2   | Objectives and Deliverables                           | 5  |

|   | 1.3   | Thesis Outline                                        | 5  |

| 2 | PMU   | J architecture                                        | 7  |

|   | 2.1   | Analog SV-RNM                                         | 9  |

|   | 2.2   | pAvIs PMU Architecture                                | 10 |

|   | 2.3   | pAvls Digital core                                    | 11 |

|   | 2.4   | pAvIs Analog core                                     | 11 |

|   |       | 2.4.1 APC RNM model                                   | 12 |

|   |       | 2.4.2 LDO RNM model                                   | 13 |

|   |       | 2.4.3 CP RNM model                                    | 14 |

|   |       | 2.4.4 Remaining PMU blocks                            | 15 |

|   | 2.5   | Model validation                                      | 15 |

|   |       | 2.5.1 Verification techniques                         | 15 |

|   |       | 2.5.2 SV's covergroup and coverpoint                  | 16 |

|   |       | 2.5.3 Coverage-driven constrained-random verification | 16 |

|   | 2.6   | Benefits of verification with UVM                     | 17 |

|   |       | 2.6.1 Verification plan                               | 18 |

|   |       | 2.6.2 Used tools                                      | 18 |

| 3 | Intro | oduction to UVM                                       | 21 |

|   | 3.1   | Overview                                              | 23 |

|   | 3.2   | The systemVerilog UVM Class library                   | 23 |

|   | 3.3   | UVM testbench and environment                         | 24 |

|   | 3.4   | Transaction-level Modelling (TLM)                     | 31 |

| 4  | 4 Implementation of UVM |          |                                                            | 35 |

|----|-------------------------|----------|------------------------------------------------------------|----|

|    | 4.1                     | Reusa    | able Universal Verification Components                     | 37 |

|    |                         | 4.1.1    | Digital UVC                                                | 37 |

|    |                         | 4.1.2    | Power UVC                                                  | 39 |

|    |                         | 4.1.3    | Regulator UVC                                              | 39 |

|    | 4.2                     | Voltag   | e regulators' UVM environment                              | 40 |

|    |                         | 4.2.1    | Sequence description                                       | 41 |

|    |                         | 4.2.2    | Scoreboards and reference models                           | 42 |

|    | 4.3                     | Digita   | core UVM environment                                       | 43 |

|    |                         | 4.3.1    | Considered UVC's                                           | 43 |

|    |                         |          | 4.3.1.A Digital UVC                                        | 43 |

|    |                         |          | 4.3.1.B SPI UVC                                            | 43 |

|    |                         |          | 4.3.1.C JTM, APC and ILIM UVC                              | 43 |

|    |                         |          | 4.3.1.D General input and general output UVCs              | 43 |

|    |                         |          | 4.3.1.E Regulator UVC                                      | 44 |

|    |                         | 4.3.2    | Sequence description                                       | 44 |

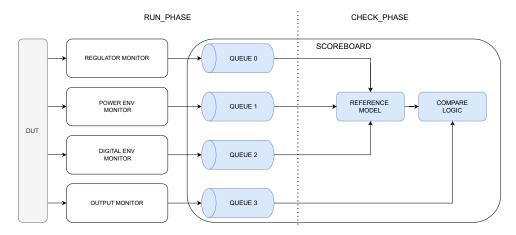

|    |                         | 4.3.3    | Scoreboard and reference model                             | 44 |

|    |                         | 4.3.4    | Proposed UVM environment architecture for the digital core | 44 |

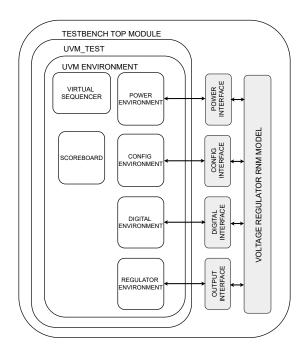

|    | 4.4                     | Power    | management unit UVM environment                            | 45 |

|    |                         | 4.4.1    | PMU start-up sequence                                      | 45 |

|    |                         | 4.4.2    | Proposed environment architecture for the PMU              | 46 |

| 5  | Res                     | ults     |                                                            | 49 |

|    | 5.1                     | Voltag   | e regulator results                                        | 51 |

|    |                         | 5.1.1    | LDO's considered coverpoints and crosses                   | 51 |

|    |                         | 5.1.2    | CP's considered coverpoints and crosses                    | 51 |

|    | 5.2                     |          | core results                                               | 52 |

|    | 5.3                     | PMU (    | core results                                               | 53 |

|    |                         | 5.3.1    | Edge Cases                                                 | 53 |

|    |                         | 5.3.2    | Edge cases results                                         | 53 |

| 6  | Con                     | clusio   | n                                                          | 57 |

|    | 6.1                     | Concl    | usions                                                     | 59 |

|    | 6.2                     | Syste    | m Limitations and Future Work                              | 59 |

| Bi | iblioa                  | raphy    |                                                            | 61 |

|    | 9                       | гарпу 61 |                                                            |    |

| A | UVIV | Code                                             | 63 |

|---|------|--------------------------------------------------|----|

|   | A.1  | Top modules                                      | 63 |

|   |      | A.1.1 UVM top module for voltage regulators      | 63 |

|   |      | A.1.2 Hardware top module for voltage regulators | 64 |

|   | A.2  | Testbench class for voltage regulators           | 66 |

|   | A.3  | Digital UVC                                      | 67 |

|   |      | A.3.1 Digital UVC environment class              | 67 |

|   |      | A.3.2 Digital sequence-item class                | 67 |

|   |      | A.3.3 Digital driver run-phase task              | 68 |

|   |      | A.3.4 Digital monitor run-phase task             | 68 |

|   | A.4  | Power UVC                                        | 69 |

|   |      | A.4.1 Power UVC environment class                | 69 |

|   |      | A.4.2 Power sequence-item class                  | 69 |

|   |      | A.4.3 power driver run-phase task                | 70 |

|   |      | A.4.4 power monitor run-phase task               | 70 |

|   | A.5  | SPI UVC                                          | 71 |

|   |      | A.5.1 SPI UVC environment class                  | 71 |

|   |      | A.5.2 SPI sequence-item class                    | 71 |

|   |      | A.5.3 SPI driver run-phase task                  | 72 |

|   |      | A.5.4 SPI monitor run-phase task                 | 72 |

|   | A.6  | Example Interfaces                               | 73 |

|   |      | A.6.1 Example Interface for digital UVC          | 73 |

|   |      | A.6.2 Example Interface for power UVC            | 74 |

|   |      | A.6.3 Example Interface for SPI UVC              | 75 |

|   | A.7  | Other relevant code listings                     | 77 |

|   |      | A.7.1 Virtual Sequences class example            | 77 |

| В | VCS  | URG coverage report                              | 79 |

|   |      |                                                  |    |

## **List of Figures**

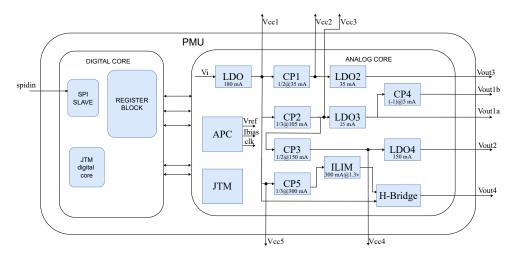

| 1.1 | PMU architecture                                                                      | 4  |

|-----|---------------------------------------------------------------------------------------|----|

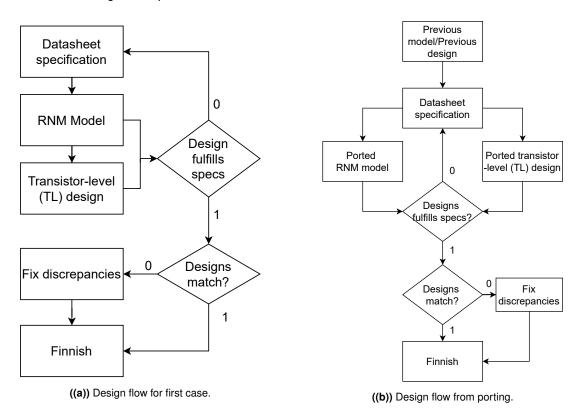

| 2.1 | Design flow with RNM models.                                                          | 9  |

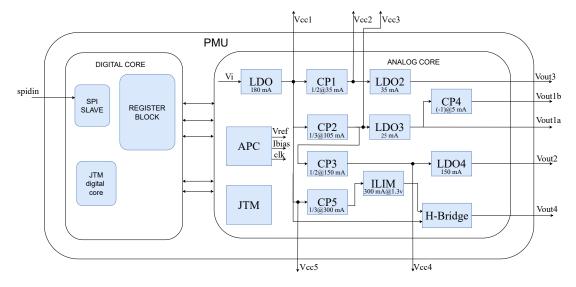

| 2.2 | PMU architecture                                                                      | 10 |

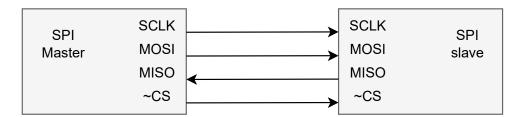

| 2.3 | Single master to single slave Serial Peripheral Interface (SPI) example communication | 11 |

| 2.4 | Advanced Power Control (APC) block diagram                                            | 12 |

| 2.5 | Low-dropout Regulator (LDO) block diagram                                             | 13 |

| 2.6 | Charge Pump (CP) block diagram example                                                | 14 |

| 2.7 | A CDV example in a UVM environment                                                    | 17 |

| 2.8 | Considered UVM-based verification plan.                                               | 19 |

| 3.1 | Typical UVM architecture                                                              | 24 |

| 3.2 | UVM phasing mechanism                                                                 | 25 |

| 3.3 | Agent block diagram                                                                   | 26 |

| 3.4 | Typical UVM architecture with virtual sequencer flow                                  | 29 |

| 3.5 | Stimulus generation and driving in the scope of UVM                                   | 29 |

| 3.6 | TLM graphical notations for producer and consumer                                     | 32 |

| 3.7 | Canonical diagram for TLM connections                                                 | 33 |

| 3.8 | TLM connections example inside an agent                                               | 33 |

| 3.9 | Monitor analysis port connection to scoreboard component                              | 34 |

| 4.1 | Universal Verification Methodology (UVM) environment for voltage regulator testing    | 41 |

| 4.2 | Block diagram of the validation                                                       | 42 |

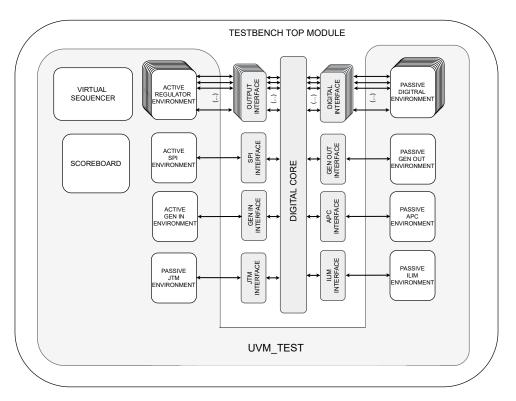

| 4.3 | UVM environment for digital core testing.                                             | 45 |

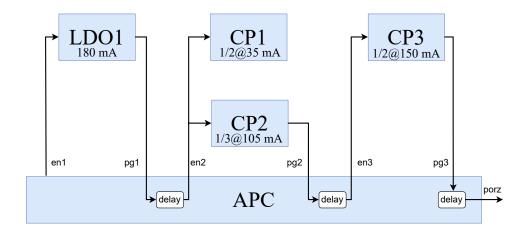

| 4.4 | PMU's start-up sequence                                                               | 46 |

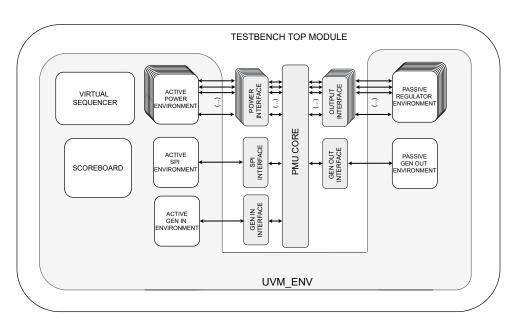

| 4.5 | UVM environment for PMU core testing                                                  | 47 |

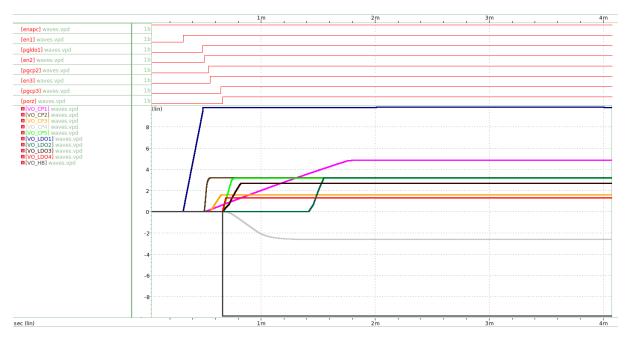

| 5.1 | PMI l's start-un sequence                                                             | 54 |

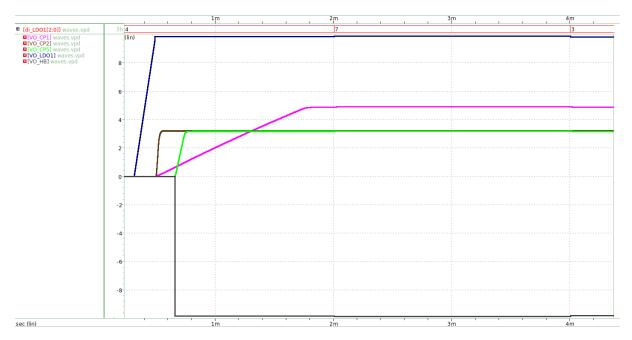

| 5.2 | Edge cases for maximum and minimum LDO1 output voltage | 55 |

|-----|--------------------------------------------------------|----|

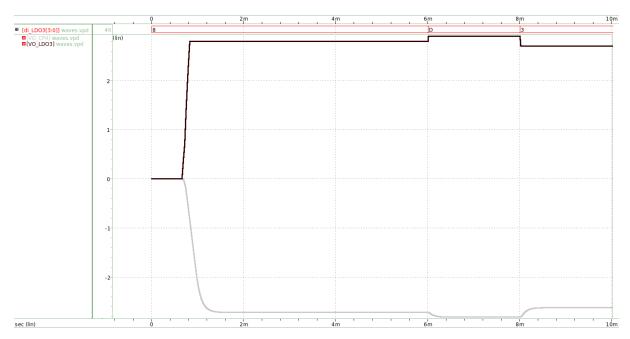

| 5.3 | Edge cases for maximum and minimum LDO3 output voltage | 55 |

## **List of Tables**

| 1.1 | PMU Specifications                                      | 4  |

|-----|---------------------------------------------------------|----|

| 2.1 | Considered power modes for the LDO                      | 14 |

| 2.2 | CP power modes                                          | 15 |

| 4.1 | Common digital interface signals                        | 37 |

| 4.2 | Common output interface signals                         | 39 |

| 5.1 | Coverage results for coverpoints and crosses of the LDO | 52 |

| 5.2 | CP coverage results                                     | 52 |

| 5.3 | Digital core coverage results                           | 53 |

## **List of Code Segments**

| 2.1  | Covergroup example                    | 16 |

|------|---------------------------------------|----|

| 3.1  | UVM agent example code                | 26 |

| 3.2  | UVM sequence_item example source code | 27 |

| 3.3  | UVM driver's run_phase task           | 28 |

| 3.4  | UVM monitor's run_phase task          | 30 |

| 3.5  | General UVM component source code     | 31 |

| A.1  | UVM top module                        | 63 |

| A.2  | Testbench top module for charge pump  | 64 |

| A.3  | Testbench top module for LDO          | 65 |

| A.4  | Testbench example for charge pump     | 66 |

| A.5  | Digital UVC class                     | 67 |

| A.6  | Digital UVC sequence-item class       | 67 |

| A.7  | Digital driver's run phase task       | 68 |

| A.8  | Digital monitor's run phase task      | 68 |

| A.9  | power UVC class                       | 69 |

| A.10 | power UVC sequence-item class         | 69 |

| A.11 | power driver's run phase task         | 70 |

| A.12 | power monitor's run phase task        | 70 |

| A.13 | SPI UVC class                         | 71 |

| A.14 | SPI UVC sequence-item class           | 71 |

| A.15 | SPI driver's run phase task           | 72 |

| A.16 | SPI monitor's run phase task          | 72 |

| A.17 | Digital interface                     | 73 |

| A.18 | Power interface                       | 74 |

| A.19 | Power interface                       | 75 |

| A.20 | Virtual sequence example.             | 77 |

## **Acronyms**

ADC Analog-to-Digital Converter

APC Advanced Power Control

API Application Programming Interface

**CDV** Coverage-driven Verification

**CP** Charge Pump

**DCIS** Conference on Design of Circuits and Integrated Systems

**DUT** Device Under Test

**EDA** Electronic Design Automation

**HB** H-bridge Regulator

HVL High-level Verification Language

ILIM Current Limiter

IO Input-output

IP Intellectual Property

JTM Junction Temperature Measurement

**LDO** Low-dropout Regulator

MCU Microcontroller Unit

MISO Master In Slave Out

MOSI Master Out Slave In

MRI Magnetic Resonance Imaging

**pAvIs** Patient and Environment Aware Adaptive Intelligent Sensor Systems

PMU Power Management Unit

**RNM** Real Number Modelling

RTC Real Time Clock

RTL Register-transfer Level

SoC System-on-a-chip

SPI Serial Peripheral Interface

SV System Verilog

**TLM** Transaction-level Modeling

**URG** Unified Report Generator

**UVC** Universal Verification Component

**UVM** Universal Verification Methodology

## 1

## Introduction

#### **Contents**

| 1.1 | Motivation                  | 3 |

|-----|-----------------------------|---|

| 1.2 | Objectives and Deliverables | 5 |

| 1.3 | Thesis Outline              | 5 |

#### 1.1 Motivation

Advances in fabrication technology and increasing time to market pressure alongside physical effects of shrinking the process technology impose greater challenges in design and testing of System-on-achip (SoC)s. Modern SoCs encompass both digital and analog blocks and require pre-silicon verification to validate their integration [1]. This approach is mandatory as multiple issues can be detected at early stages, aiming for first-time right silicon, saving time and resources. Analog and digital simulation exist in different domains [2]. Analog verification is an ad-hoc complex procedure that performs computation of large data structures with no obvious signal flow pattern, therefore lacking of a standardized methodology [2]. On the other hand, digital verification is powered with versatile tools that allow for testbench automation, constrained-random stimulus generation, coverage collection and much more. To improve the accuracy of the analog model representation, Real Number Modelling (RNM) is used to quantify analog behavior in the relevant wires. Analog behavior is described as real data, where floating point numbers are used. This approach relies on a digital solver to achieve near-digital verification speeds and improves the pre-silicon verification time when compared to transistor-level simulation. By adopting this methodology, full-chip verification is facilitated for a large scale of mixed-signal designs and the methodologies applied for digital testing can be ported and adapted to fit a mixed-signal design. These behavioral models are also important as they are rapidly produced and independent of the process technology.

Innovation and frequent new projects that benefit from reusability of previously designed Intellectual Property (IP) generate situations where test environments can be easily adapted and ported to new projects. Universal Verification Methodology (UVM) provides the infrastructure to explore this methodology. UVM proves to be an improvement for traditional mixed-signal and digital verification methods as it provides constrained-random coverage-driven test environments. It allows for test automation granting high configurability, interoperability and Coverage-driven Verification (CDV). Directed tests can also be explored by UVM as it provides a robust methodology for test generation. Testbenches can be designed for reusability reducing the effort when migrating components for different projects.

Combining UVM and RNM enables high-performance mixed signal SoC verification. RNM is limited for analog verification, but excels when integrated in a verification environment based on functional and coverage-driven verification. In a mixed-signal design, one can use it to imitate the analog counterpart of the SoC which enables extensive testing and increased simulation speeds. This verification level would not be possible for a pure embedded analog design.

Patient and Environment Aware Adaptive Intelligent Sensor Systems (pAvIs) European project [3] aims to develop innovative approaches in improving the electronics and intelligent sensor systems for professional healthcare diagnosis. Magnetic Resonance Imaging (MRI), computed tomographic and ultrasound imaging are some of the examples. The objective of this effort is to improve the current one-

size fits all paradigm, to sensor-based systems capable of diagnosing diseases, monitoring or enabling the restoration of physiological functions, or treating adverse medical conditions. This approach provides greater adaptability to an individual patient and the operating environment, providing personalized diagnosis and treatment.

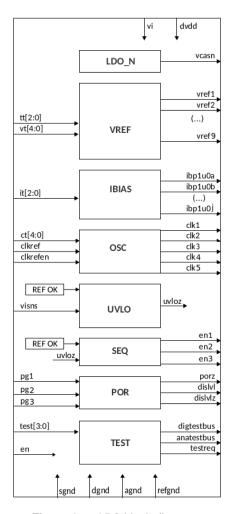

SiliconGate and Instituto Superior Técnico are designing a Power Management Unit (PMU) (Figure 1.1) of an intelligent sensor system for a MRI machine with mixed-signal processing IPs at its core for the pAvIs project. These sensors will be embedded in an environment with strong electromagnetic fields, which require specialized design and testing techniques to obtain a fully functional and robust integrated circuit.

Figure 1.1: PMU architecture.

Table 1.1: PMU Specifications.

| Symbol            | Min    | Тур         | Max    |

|-------------------|--------|-------------|--------|

| $V_{in}$          | 10 V   | 12 V        | 14 V   |

| freq              | -      | 540/145 MHz | -      |

| out1a             | 2.7 V  | 2.8 V       | 2.9 V  |

|                   | 0 mA   | 13 mA       | 20 mA  |

| out1b             | -2.9 V | -2.8 V      | -2.7 V |

|                   | 0 mA   | 1 mA        | 5 mA   |

| out2              | 1.3 V  | 1.4 V       | 1.5 V  |

|                   | 0 mA   | 100 mA      | 150 mA |

| out3              | 3.2 V  | 3.3 V       | 3.4 V  |

|                   | 0 mA   | 25 mA       | 35 mA  |

| out4 <sup>a</sup> | -9.9 V | -11.9 V     | 13.9 V |

|                   | 0 mA   | 0.1 mA      | 1 mA   |

| out4 <sup>a</sup> | 1.3 V  | 2 V         | 2.6 V  |

|                   | 0 mA   | 160 mA      | 300 mA |

<sup>&</sup>lt;sup>a</sup>out4 output has two modes of operation.

A UVM-based architecture for a RNM model of PMU and its components is presented in this thesis using the pAvIs project as an example. This architecture is used for the validation of voltage regulators and digital core within the model and their integration to fit the specification of the PMU, described in table 1.1. The implementation, previously defined for the PMU, is presented in Figure 1.1.

#### 1.2 Objectives and Deliverables

The purpose of this work is to implement a functional UVM environment for testing and validation of a RNM model of voltage regulators and to validate their integration in a PMU presenting, as an example, the pAvIs project.

The work developed in this thesis resulted in a paper accepted for poster presentation in the XXXVII Conference on Design of Circuits and Integrated Systems (DCIS) proceedings.

#### 1.3 Thesis Outline

Chapter 2 introduces RNM design flow and describes the PMU architecture. RNM models are described for analog core components. Constrained-random and CDV concepts are also described. Conventional model validation approaches are assessed, showing their limitations and the advantages of adopting UVM.

Chapter 3 presents an overview of UVM and previous studies and applications. Furthermore it displays an introduction to UVM concepts and their roles in the model verification environment. Transaction-level Modeling (TLM) concepts are also introduced.

In Chapter 4, the implementation of the UVM architecture is explained for voltage regulators and digital cores. An environment to test the whole PMU is also described.

Chapter 5 shows the results and comparisons to the adopted standard System Verilog (SV) flow.

Chapter 6 presents the conclusions of this work, identifies limitations of UVM and lists encountered problems. Suggestions for future work on the matter are outlined.

# 2

## **PMU** architecture

#### **Contents**

| 2.1 | Analog SV-RNM                     |

|-----|-----------------------------------|

| 2.2 | pAvls PMU Architecture            |

| 2.3 | pAvls Digital core                |

| 2.4 | pAvls Analog core                 |

| 2.5 | Model validation                  |

| 2.6 | Benefits of verification with UVM |

## 2.1 Analog SV-RNM

When designing mixed-signal circuits it is essential to perform a translation from the specification to the real transistor-level implementation. A verilog model of the mixed-signal circuit is also frequently designed using RNM for key parameters. SV RNM models are of extreme importance for this transition between specification and transistor-level design, as they are responsible to ensure that the design fits the specification and that the integration of digital and analog counterparts is properly implemented.

The verilog model of mixed-signal circuits can be designed in two different contexts. This first one (Figure 2.1(a)) depicts the scenario where the RNM model is built for the first time, only based on the datasheet specification. In this case the RNM model is only built to meet the specification. The analog design team develops the transistor-level circuit to be in accordance with the RNM model and, consequently, in accordance with the datasheet specification.

The second scenario (Figure 2.1(b)) is the one where the RNM models and transistor-level designs are independently ported from a previously existing project. In this scenario, design features and parameters must be updated to fit the new project's datasheet for both RNM model and transistor-level design. At the end both design must present the same behavior.

Figure 2.1: Design flow with RNM models.

When the transistor (or gate) level schematic already exists, the extraction of the corresponding

schematic is very useful for the verilog model design since it contains the high level structure of the design. Moreover digital cells are already automatically converted to SV logic function and need no further changes. The analog behaviour is the one to model as analog signals are described using a discrete representation, defining the analog counterpart as a signal flow event-driven model. For the scope of behavioral verification information such as supply verification and threshold values, evolution of the output voltage through an output capacitance model (when applicable) and definition of other output signals, RNM provides an accurate representation of each component functional behavior. All these features are described with SV primitives. Analog signals are driven as 64 bit floating point numbers, and converted to real numbers to perform computations (\$bitstoreal and \$realtobits serve as conversion tools).

As stated in section 1.1, verilog models introduce an abstraction layer in the design, loosing certain details of analog behavior and complexity. This enables extensive high-speed simulation that, when well explored, results in a more robust validation mechanism.

#### 2.2 pAvIs PMU Architecture

A PMU is the circuit responsible for power management of an SoC. Its main roles consist of generating reference voltages, controlling power modes, battery charging, DC to DC conversion and other auxiliary functions to control the power flow. Generally, SoCs powered by a PMU require multiple voltage domains and can also be supplied from multiple power sources which define multiple requirements for operation of the PMU. The architecture of the pAvIs PMU is displayed on Figure 2.2.

Figure 2.2: PMU architecture.

#### 2.3 pAvIs Digital core

The pAvIs PMU possesses a digital core that encapsulates a register bank to store and configure digital control bits for the IPs inside the analog core. The digital core also receives input signals from the analog core to ensure observability and awareness of the status of the PMU internal voltages. The register bank is composed of thirteen 32-bit registers, that store configuration bits for each IP and other PMU control bits.

#### **SPI** protocol

The Serial Peripheral Interface (SPI) protocol [4] is a synchronous communication interface. It adopts a master-slave architecture, usually with one master and with one or multiple slaves. The master controls read and write operations on a register bank.

To begin communication the master defines the clock frequency, selects the slave with the chip select bit and initiates the serial communication through the Master Out Slave In (MOSI). The slave reads the bit and and sends it through the Master In Slave Out (MISO) interface resulting in a full-duplex communication. Figure 2.3 exemplifies a generic block diagram of an SPI communication protocol with one master and one slave.

The SPI protocol is used to establish the communication from the PMU interface and the top module. The PMU digital core defines a module which handles the implementation of the protocol, acting as the slave component.

Figure 2.3: Single master to single slave SPI example communication.

The implemented SPI communication protocol for the PMU starts with the master sending an operation selector bit (read operation as logic low and write as logic high), followed by the chip select bit. Then the 6-bit address bus is driven through the MOSI interface followed by the 32-bit data bus.

## 2.4 pAvIs Analog core

The pAvIs analog core is composed of an Advanced Power Control (APC), four Low-dropout Regulator (LDO)s, five Charge Pump (CP)s), a Junction Temperature Measurement (JTM) regulator, a Current

Limiter (ILIM) and an H-bridge Regulator (HB).

#### 2.4.1 APC RNM model

The APC generates control signals that coordinate the start-up sequence and overall functionality of the PMU, representing the backbone of the PMU. It generates enable signals reference voltages, bias currents and other control signals. Each regulator start-up is complete when it returns the power good (*pg*) indicator to the APC. Only after this bit is held high is the APC allowed to enable the next regulator. Generated reference voltages and currents can be digitally trimmed for increased performance.

A representative block diagram for pAvIs APC is shown in Figure 2.4.

Figure 2.4: APC block diagram.

The APC model is designed as a SV behavioral Register-transfer Level (RTL) description combined with extracted views of a ring oscillator for clock generation, a bandgap circuit, and a clock division block. This inevitably results in a simplified description of the analog design. To emulate the time related with

the rising of reference voltages, debouncer circuits, or propagation of combinational logic, expected time stamps are considered, which suffices in the scope of behavioral verification. Reference voltages and currents are defined as real numbers with a 64-bit representation for each regulator with the respective trimming features. Enable output signals are generated taking into account the startup sequence, and respective power good indicators (*pg*), which culminate in the release of the *porz* (power on reset, active low) signal, which enables the system level converters. A test block is also designed with the purpose of adding controllability and observability to internal APC nets.

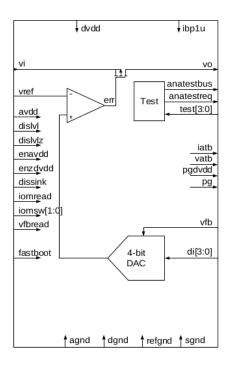

#### 2.4.2 LDO RNM model

The LDO is a regulator that provides a constant output voltage, even when the supply voltage is close to the output voltage. LDO's, and voltage regulators in general, include configurable features that are controlled through a digital port. A block diagram for the LDO is displayed in Figure 2.5.

Figure 2.5: LDO block diagram.

The LDO model is a pure behavioral RTL design. The definition of the programmable output voltage is configured at the digital input di.

In table 2.1, the considered power operating modes of the LDO model are presented. The output pin pg is set to high when the output voltage reaches 95% of the programmed voltage. pg is reseted when the output voltage is lower than 90% of the programmed value.

Table 2.1: Considered power modes for the LDO.

| enavdd | enzdvdd | dislvl | pg/pgdvdd     | power                   |  |

|--------|---------|--------|---------------|-------------------------|--|

| 0      | x       | Х      | 0/0           | power down              |  |

| 1      | х       | 1      | normal/0      | enabled w/def. settings |  |

| 1      | 0       | 0      | normal/normal | enabled                 |  |

| 1      | 1       | 0      | 0/0           | power down              |  |

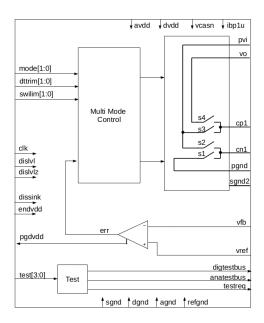

#### 2.4.3 CP RNM model

The charge pump is a switched capacitor circuit that regulates the output voltage using predefined ratios of the input and/or output voltage. It possesses a digital control logic that acts on switches to explore charge transfer between capacitors. A block diagram for the CP is displayed in Figure 2.6.

Figure 2.6: CP block diagram example.

The charge pump model top representation is extracted from the design schematic. The control block and generation of non-overlapped switching clocks consist of logic gates which are converted in SV logic representation. The power, voltage divider, and comparator blocks are replaced by simplified RNM behavioral models which implements the relevant behavior at a high level of abstraction.

The power block represents the backbone of the charge pump. For each topology, the model defines the switching configuration. For each configuration, the model explicitly computes the capacitor currents taking into account resistive losses through bond wires and switches and current limitation features. The currents serve as input of SV capacitor models (flying capacitor and output capacitor) that describe the evolution of the output voltage. The pg and pgdvdd functionality is the same as the LDO. For the different power modes pg and pgdvdd are expected to have the values represented in table 2.2. A test

block is also included in the CP.

Table 2.2: CP power modes.

| endvdd dislvl |   | pg/pgdvdd     | power      |  |

|---------------|---|---------------|------------|--|

| Х             | 1 | 0/0           | power down |  |

| 0             | 0 | 0/0           | power down |  |

| 1             | 0 | normal/normal | enabled    |  |

The PMU analog core has three different charge pump topologies (see Figure 2.2). Charge pumps 2 and 5 implement a division by 3. Charge pumps 1 and 3 implement a division by 2 and charge pump 4 implements an inverter topology.

### 2.4.4 Remaining PMU blocks

The JTM is a high resolution Analog-to-Digital Converter (ADC) for temperature, voltage and current monitoring.

The HB specifies two modes of operation for one of the outputs of the PMU (see table 1.1). A current mode, where the model outputs a current through the pin and a voltage mode where it defines a positive or a negative voltage through the output pin.

The ILIM IP limits the current capping the output current for the HB current mode to 300 mA.

These regulators and the APC were not individually tested with UVM. Instead, they were tested with traditional SV flow.

#### 2.5 Model validation

#### 2.5.1 Verification techniques

The most basic SV verification environment consists of stimuli being driven to the Device Under Test (DUT) with the intention of performing a self driven verification by the engineer. The verification process relies on viewing waveforms through a wave viewer software and individually verifying every output of the design.

An improved version of this methodology explores an implementation of self-checkable processes which makes use of SV features such as the wait() statement and verification of parameter thresholds with printed messages upon failure. Currently at SiliconGate self-checkable processes are commonly used for functional verification.

Both verification approaches depend solely on the thoroughness of the verification plan and the individuals responsible for the development of the test environment. Given a certain specification for a certain IP, the test engineer generates a set of stimuli to functionally exercise the DUT.

UVM aims to consolidate the verification process, providing a robust verification environment with a well defined structure purposely built to explore extensive coverage-driven, constrained-random and self-sufficient testbenches. It possesses specialized tools to automate test generation and systematize self-checkable processes and coverage collection mechanisms.

#### 2.5.2 SV's covergroup and coverpoint

SV defines covergroups as a user-defined type built to define the specification for a coverage model. A covergroup contains coverpoints that specify a certain statement to be covered, a set of cross coverage between coverage points, an event that defines when to sample the covergroup and other options to configure the object. When a coverpoint is defined, a set of bins is generated, which contain all possible combinations for the considered coverpoint variable. For instance, a "n" bit coverpoint variable results in  $2^n$  automatically generated bins. It is also possible to explicitly define bins for a coverpoint. When the user crosses two coverpoints all combinations of bins for both coverpoints are generated. An example covergroup is defined in source code 2.1.

**Source Code 2.1:** Covergroup example.

In the *cover\_example* covergroup, 3 coverpoints are defined. For the enable\_mode coverpoint, an explicit bin is represented, defining considered modes for the coverage model.

#### 2.5.3 Coverage-driven constrained-random verification

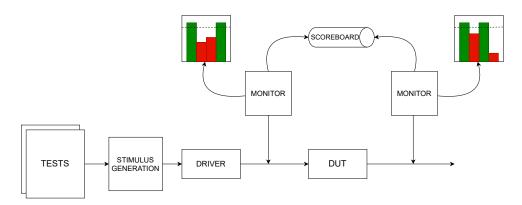

Coverage-driven verification (CDV) is a verification methodology based on defining a strategy for verification. As the name implies, it is based in coverage control as building a verification plan beforehand diminishes the time needed to successfully verify a design. Figure 2.7 illustrates a coverage collection example in UVM. The monitors capture transactions from the DUT interfaces and alongside pre-defined SV coverage model, assess if all test scenarios were exercised on the DUT.

Figure 2.7: A CDV example in a UVM environment.

The goal of constrained-random is to create transactions that allow the DUT to operate in meaningful scenarios where results can be used to improve the current constraints aiming for a coverage goal and validation of the correct behavior of the DUT. CDV is useful as it thoroughly stresses the DUT and, when coupled with a scoreboard validation, results in a robust verification mechanism as all considered test scenarios are validated.

#### 2.6 Benefits of verification with UVM

Standard SV test implementation is not the most effective, as directed tests are adopted and specifically made to validate the behaviour of design features lacking of coverage collection mechanisms and standardized ways of finding unexpected behaviour of models. UVM is introduced in chapter 3.

The verification process is not automated and porting test environments from previous projects is an exhaustive and repetitive process.

UVM provides the infrastructure to automate testbench generation, benefiting from its predefined Universal Verification Component (UVC)s. The scoreboard component alongside monitors and a reference model, validate the outputs of the DUT during run-time, generating UVM reports for miscompares and detailing the input stimuli which resulted in unexpected results. Detailed coverage reports are generated with the Unified Report Generator (URG) VCS tool, which accelerates the process of reaching coverage goals (Annex B shows an example coverage report). Some IPs are not as thoroughly tested as others, hence, this standardized building mechanism allows for conventional and robust test environments, granting the same level of verification for all DUTs.

Besides, the randomization of test sequences allows the environment to exercise the DUT with input stimuli which were not considered in the verification plan. This approach is prone to identifying defects in the model, which can be reported to the design team.

In short, UVM verification provides the following advantages when compared to traditional SV verifi-

#### cation:

- Modularity and reusability: The methodology defines modular components enabling easier replacement policies within the components of the same type (same level of abstraction) and across projects (from single IPs to PMUs), as well as across projects.

- 2. **Separating tests from testbenches**: Generated sequences (stimuli set) are defined inside the encapsulated environment and can be reused across different projects.

- 3. **Sequence generation methodology**: This methodology provides control on how stimuli is generated. E.g., sequences can be randomized, directed, layered and included in virtual sequences.

- 4. **Configuration**: The UVM hierarchy is deep and well defined. The configuration mechanism provides a standardized well structured way of configuring different testbench components.

#### 2.6.1 Verification plan

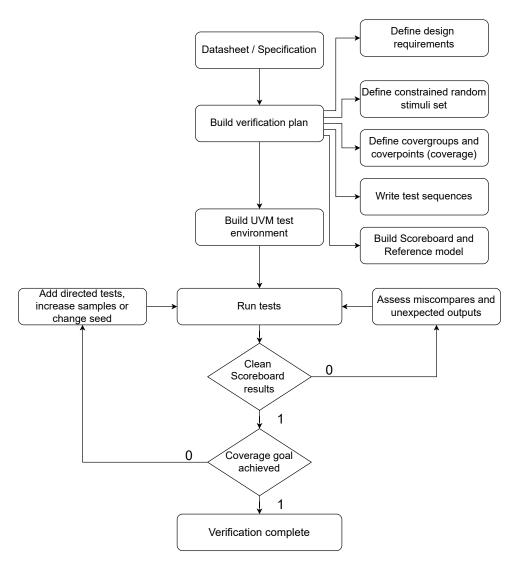

The verification plan is shown in Figure 2.8. The datasheet allows the generation of the SV model, reference model and verification plan. Based on this information the designer defines the constrained-random stimuli set and covergroups to assure that all considered test scenarios are exercised. Test sequences are generated for each input variables with aim to achieve full functional verification and 100 % code coverage. Fully pseudo-random test sequences are also described and included in the verification process. The scoreboard, reference model and monitors determine the success of the verification plan, aiming for coverage milestones and clean scoreboard UVM reports.

#### 2.6.2 Used tools

Accelera provides an Application Programming Interface (API) standard for UVM and a reference implementation which constists of a class library defined with SV.

Cadence<sup>®</sup> Virtuoso<sup>™</sup> and Synopsys<sup>®</sup> Custom Compiler<sup>™</sup> Schematic Editors are tools that allow the design of integrated circuits capable of genererating SPICE netlists and extracting SV models based on pre-built libraries.

Synopsys<sup>®</sup> VCS<sup>™</sup> functional verification solution is the engine used for compilation.

Synopsys<sup>®</sup> WaveView <sup>™</sup> is a waveform visualizer, useful for debugging purposes.

Figure 2.8: Considered UVM-based verification plan.

# 3

# Introduction to UVM

#### **Contents**

| 3.1 | Overview                            | 23 |

|-----|-------------------------------------|----|

| 3.2 | The systemVerilog UVM Class library | 23 |

| 3.3 | UVM testbench and environment       | 24 |

| 3.4 | Transaction-level Modelling (TLM)   | 31 |

#### 3.1 Overview

RNM [5] allows the description of mixed-signal designs analog behaviour [6, 7], enabling signal flow event-driven models using High-level Verification Language (HVL). This approach inevitably imposes limitations, but builds the foundation for Coverage-driven Verification (CDV), [8], [9] and functional verification. Functional verification consumes a significant time of the project, [10]. Additionally, when aiming for functional verification, several test scenarios might not be considered.

UVM is the current standard methodology for verifying digital and mixed-signal designs. With its structured library classes, it allows the creation of constrained-random coverage-driven environments benefiting from SV object-oriented features, [11]. It has become the industry standard for hardware verification as it is supported by the main Electronic Design Automation (EDA) vendors and adopted worldwide for digital and mixed-signal IP testing.

An example application of UVM for a RNM design was presented for an ADC [12]. In this work, the use of UVM alongside RNM is illustrated for the validation of an ADC and its components.

UVM has been used to test the supply module of a Microcontroller Unit (MCU) inside a Real Time Clock (RTC) to enter or exit the ultra-low power modes [13]. However, in this work, only the RTC functionality was targeted with the UVM validatio, and no voltage regulation IP cores were tested. In the previous publication based on this thesis work [14], an application of UVM to test voltage regulators was implemented. The use of UVM to validate verilogAMS models was also addressed in [15] and [16]. The reliability of these approaches was also assessed [16], where advantages and disadvantages were explicitly defined.

Another relevant project explores a UVM CDV environment to test the implementation of a SPI protocol [8], as a similar approach is considered for validating the same SPI communication protocol inside the pAvIs' PMU core.

Combining RNM with UVM for mixed signal IP verification [12], [17], enables testbench automation, coverage collection and increased simulation speeds.

# 3.2 The systemVerilog UVM Class library

The UVM class library has several predefined classes, utilities and macros required for verification. It eases the development and reusability of verification environments [18], [19]. Components are derived from these base classes and inherit their properties, granting them great configurability and a standardized coding style.

As stated in [18], there are two great advantages when adopting the UVM class library:

The encapsulation of important verification features such as, printing, copying, test phases, factory

methods, and more.

• The possibility to derive all components displayed in figure 3.1 from these pre-defined classes, increasing readability of the code and granting a robust and well defined hierarchical structure.

The UVM class library also provides a shared database to ease configurability (uvm\_config\_db), a user-controllable messaging utility for failure reporting, a standard communication infrastructure (TLM) and a flexible construction mechanism (UVM\_FACTORY).

#### 3.3 UVM testbench and environment

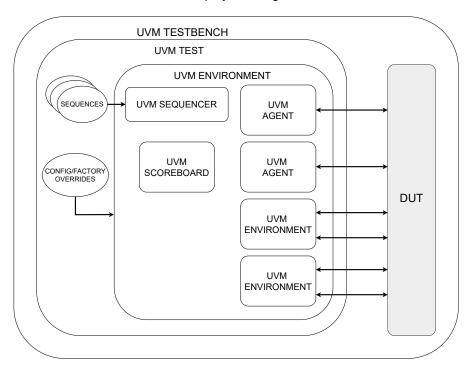

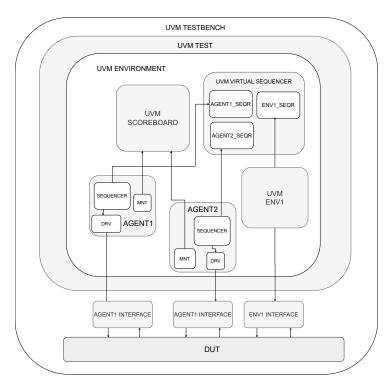

A typical UVM testbench architecture is displayed in Figure 3.1.

Figure 3.1: Typical UVM architecture

To briefly introduce UVM, some important concepts are explained below.

- Testbench top module The testbench represents the top level of the hierarchy. It instantiates the UVM test environments, interfaces, DUT and other key components and coordinates the testing procedure. Annex A.1 shows examples for the considered top modules of this project.

- Test Specifies the test scenario for the testbench. It instantiates the environment (uvm\_env) and environment configuration properties [12]. An example UVM environment is shown in annex A.2.

Several test environments can be instantiated for the same DUT.

- UVM environment Derived from the base class uvm\_env, it is a key building block of UVM test environment and system verification. The uvm\_env provides a set of features that allow the re-usability and flexibility of the environment. The environment may have multiple agents for different interfaces, a common scoreboard, a functional coverage collector and even other environments. It is responsible to integrate all the henceforth described components and coordinate sequence generation, monitoring and coverage checking of the DUT.

- UVC A UVC represents a self contained, plug'n'play verification environment for a specific interface or a generic IP. It consists of one or more configurable agents with a predefined set of sequences that translates to test stimuli, coverage model and comprehensive failure report protocol based in UVM. Annex A.3 shows an example UVC.

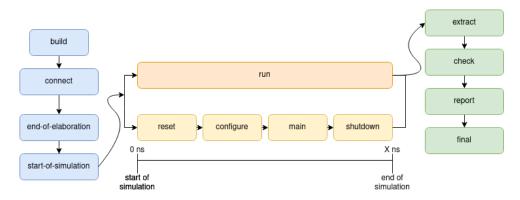

- Phase UVM controls the creation, configuration and execution of a simulation run using phases. Figure 3.2 shows a graphical representation of UVM phases. Phasing acts as a synchronization mechanism. Only after each component successfully finishes their execution in a phase, is the control flow allowed to proceed to the next phase. This creates a very structured and intuitive set of events. All phases can be grouped into three main phases: build-time phases, run-time phases and clean-up phases. The build, connect, end-of-elaboration and start-of-simulation phases are entry

Figure 3.2: UVM phasing mechanism.

level phases that are responsible for creating, connecting and configuring the test environment. The run\_phase, is the only phase that consumes simulation time, executing stimuli on the DUT. Parallel to the run-phase, UVM provides optional runtime sub-phases to give more control over stimuli during the run-phase.

The phases extract, check, report and final are exit phases which run at the end of the simulation to check scoreboards and report results.

Phasing functions have to be explicitly described under a class scope so that their execution is considered during a simulation run.

There are components in the hierarchy that concentrate their execution under specific phases, e.g. the scoreboard examines results in the check-phase and and ouputs information in the report-phase.

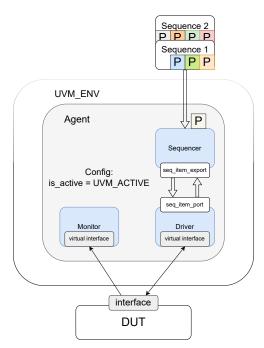

• Agent - The agent, derived from the uvm\_agent class, encapsulates a driver, a sequencer, a monitor and a collector(when applicable). By doing so, it binds these components together to drive, monitor and collect coverage from the DUT or specific ports of the DUT. This represents an essential abstraction layer as it eases the integration of these components in the environment. An Agent can be active, if it drives signals to the DUT, or passive, if it only monitors the ports of the DUT. For this purpose the agent possesses a variable called is\_active which is accessible from the UVM\_environment. When set to UVM\_ACTIVE the agent is set to active and is composed of a driver, sequencer and a monitor. If the variable is set to UVM\_PASSIVE, the agent is set to be passive and only has a monitor. A representative block diagram for a generic active agent and its flow is displayed in Figure 3.3.

Figure 3.3: Agent block diagram.

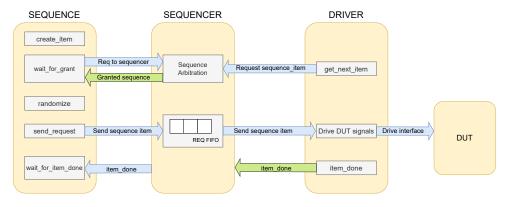

The sequence (represented as P in Figure 3.3) exemplifies a pattern of signals (sequence-items) to be driven to the DUT. The sequencer retrieves, randomizes and sends sequence-items to the driver on demand. The driver implements the protocol to drive signals to the DUT and communicates a item\_done flag to the sequencer once the data transfer is done.

The Source Code 3.1 represents an example UVM code for a generic agent.

Source Code 3.1: UVM agent example code.

```

class example_agent extends uvm_agent;

driver

example_driver ;//handles

monitor example_monitor ;

sequencer example_sequencer;

function void build_phase(uvm_phase phase);

super.build_phase(phase);

monitor = output_monitor::type_id::create("monitor", this);

if(is_active == UVM_ACTIVE) begin

driver = output_driver::type_id::create("driver", this);

sequencer = output_sequencer::type_id::create("sequencer", this);

end

`uvm_info("MSG", "Agent build_phase",UVM_HIGH)

endfunction : build_phase

function void connect_phase(uvm_phase phase);

if(is_active == UVM_ACTIVE)

driver.seq_item_port.connect(sequencer.seq_item_export);

endfunction : connect_phase

endclass

```

The connect phase function implements the TLM connection between driver and sequencer. TLM is analyzed in detail in section 3.4.

Sequence-item - Derived from the uvm\_sequence\_item base class, sequence-items represent stimuli and transactions of the UVM environment. A set of attributes, constraints and methods can be defined for the sequence-item for it to fit the needs of the DUT or the transaction type and mold the data. An example sequence-item class is presented in source code 3.2.

**Source Code 3.2:** UVM sequence\_item example source code.

```

`uvm_field_int (anatestreq , UVM_ALL_ON )

`uvm_object_utils_end

// Define packet constraints

endclass: example_packet

```

- Sequence A sequence, derived from the uvm\_sequence class, describes a bundle of transactions (sequence-items) or other sequences. To generate sequences, UVM provides a set of macros that implement the standard flow of transaction generation. These macros encapsulate a set of methods in a single call and cover different possible scenarios for sequence generation, easing the process. Sequences are type-parameterized to a sequence\_item which represents the transaction to be generated by the sequencer. Annex A.7.1 depicts an example application for virtual sequences.

- Sequencer A sequencer, derived from the uvm\_sequencer class, is responsible for sequence generation and controls the items to be sent to the driver. It generates data on-demand and returns them to the driver, as one can see in Figure 3.3). The randomization process can be controlled by setting constraints in the sequence-item model. Sequencers can exist inside agents, where their scope is local for the agent, or inside test environments as virtual sequencers. A virtual sequencer has handles to other sequencers of the environment, as shown in Figure 3.4. In this case it provides a centralized sequence generation mechanism, coordinating different elements of the environment.

- Driver The driver, derived from the uvm\_driver class, is connected to the DUT via a virtual interface and drives stimuli to its ports. Similarly to the sequencer, the driver is type-parameterized to a sequence-item that possesses the information to be driven to the DUT. During the run\_phase task, the driver decodes the transaction to obtain the signals and consume simulation time to forward the data. A generic example for a driver's run\_phase task is displayed in source code 3.3.

Source Code 3.3: UVM driver's run\_phase task.

```

task run_phase(uvm_phase phase);

//req is a handle which represents the transaction

seq_item_port.get_next_item(req);//pull item from the sequencer

send_to_dut(req);//drive function

seq_item_port.item_done();//communicate item done to the sequencer

endtask : run_phase

```

These method calls implementation (source code 3.3) is detailed in Figure 3.5. Create\_item creates the sequence-item. Wait\_for\_grant is a blocking method which blocks execution until it receives the

Figure 3.4: Typical UVM architecture with virtual sequencer flow.

get\_next\_item request from the driver. The sequence-item is then randomized and forwarded to the driver that translates to verilog synthesizable logic signals and drives them to the DUT. Finally, item\_done signals the end of the transaction.

Figure 3.5: Stimulus generation and driving in the scope of UVM.

• Monitor - The monitor is a passive component in the environment. It retrieves signals from the DUT (or, in some cases, from a collector) and sends them to a scoreboard or other UVM components to perform behavioural and procedural validation. Monitors are also used to perform coverage control in order to cover several test scenarios. During the run\_phase, the monitor collects data from the interface and performs housekeeping to proceed with data validation and coverage assessment.

Similarly to the driver, the connection to the DUT is made via a virtual interface.

In Figure 3.4, monitors inside active agents connect to a scoreboard component sending transactions that were previously retrieved from the virtual interface. A generic example for a monitor's run\_phase task is displayed in source code 3.4.

Source Code 3.4: UVM monitor's run\_phase task.

```

task run_phase(uvm_phase phase);

collect_transaction();

send_to_scoreboard();

update_coverage();

endtask : run_phase

```

- Virtual Interface The virtual interface represents an abstraction layer as it represents a pointer

to an actual interface. It allows the defined classes to access the DUT ports while promoting

reusability. Annex A.1.1 shows and example of a UVM top module where the connection of virtual

interfaces to an actual interface are established. Annex A.6.1 depicts an actual SV interface.

- Scoreboard The scoreboard, derived from the uvm\_scoreboard class, verifies if the DUT outputs the expected results. It retrieves information from monitors and, alongside a reference model, checks the correctness of the DUT outputs. The uvm\_scoreboard is built with robust failure reporting features. UVM provides a set of report macros that, when correctly implemented, can extensively monitor the execution of the simulation run. This reporting mechanism takes into account severity, verbosity and simulation handling behavior, being each of them independently specified and controlled. It is intended to make the scoreboard as self-governing as possible, outputting detailed information when needed. The most commonly used macros are uvm\_info, uvm\_warning, uvm\_error and uvm\_fatal. Severity, as the name implies indicates importance, verbosity indicates filter level and simulation handling refers to the action taken by the simulator which depends on the severity being produced on the verification environment.

- Reference model The reference model emulates the behaviour of the DUT generating the correct output for a specific input. These results are afterwards used by the scoreboard to evaluate the DUT's output.

- Factory The UVM factory provides a standardized way of replacing an existing class by any of

its inherited child classes. Upon creation, objects are registered in the factory with UVM defined

macros. Once registered, the factory provides flexibility allowing the user to override certain types

and instances of class objects by its child types. To enable the factory's full functionalities, the

create static method must be used on the creation of the object instance. Then the user can call one of the set\_type\_override macros to perform the replacement.

A typical UVM component is defined in the Source code 3.5.

Source Code 3.5: General UVM component source code.

```

class example extends uvm_component;

`uvm_component_utils(example)//utility macro

function new (string name, uvm_component parent);//constructor

super.new(name,parent);

endfunction : new

type example_type; //handle for object creation

function void build_phase(uvm_phase phase);//phasing

super.build_phase(phase);

example_type = type::type_id::create("example_type"

, this);

`uvm_info("MSG", "Example of how to implement a print in UVM",UVM_HIGH)

endfunction

endclass : example

```

Classes are extended from predefined classes and inherit their features. In this example, the uvm\_component\_utils() macro enables automation and registers the class to the uvm\_factory. All classes must have a constructor which is responsible for creating the object instance and building the hierarchical structure (new function). The user can add functions required to mold the data or collect information while performing tests.

The build\_phase represents a UVM pre-defined function which is related to the phasing schema. Inside this function, there is an example of how to create a new object that complies with the uvm\_factory requirements. There is also an example of a uvm\_info macro that prints UVM compliant messages. The third argument of the uvm\_info macro defines verbosity. Verbosity is used to filter what is printed during a run in order to only output relevant information to keep track of the execution phases or to aid in the debugging process.

# 3.4 Transaction-level Modelling (TLM)

UVM benefits from TLM [18], [19], as it provides an intuitive level of abstraction as stimuli is thought on the transaction-level instead of signal-level stimuli. This leads to faster simulation time as transactions simulate faster than RTL models, also benefiting from broader reusability as transactions tend to be more

flexible. Combined with UVM and its flexible, phased infrastructure, TLM promotes great interoperability between components and more coherent replacement policies.

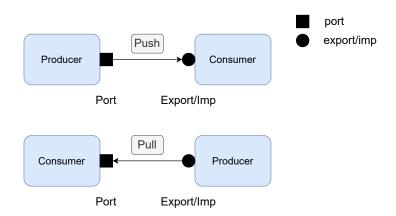

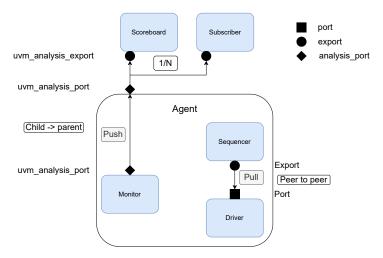

UVM ports and exports are used to send transaction objects cross different levels of testbench hierarchy. UVM ports initiate and forward packets to upstream layers and exports accept and forward packets from top layers to destination. TLM provides a graphical notation for different types of communication (Figure 3.6). The transaction can happen on the direction producer to consumer or vice-versa. In the first case the data flow happens in the same direction of the control flow (push connection example in Figure 3.6) and in the latter, the data flows in the opposite direction of the control flow (pull connection example in Figure 3.6).

Figure 3.6: TLM graphical notations for producer and consumer

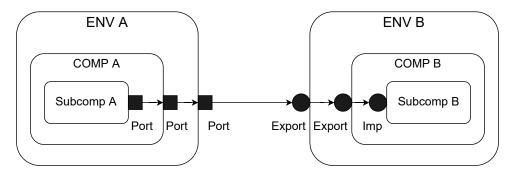

As an example, consider the Figure 3.7, that represents a canonical diagram for TLM connections. On the left hand side (Env A), ports and calls to a push connection going up the hierarchy are illustrated. On the right hand side, exports are illustrated with a push connection going down the hierarchy.

Exports differ from imps as they provide a way point in a series of TLM calls whereas the imp provides the end of the line of a TLM connection where the call will actually be implemented. This is depicted on the right hand side of Figure 3.7 (Env B). Hence, if the component implements an export, it passes the transaction to a child component. If the component has an imp it must itself provide an implementation of the correspondent task or function. Connection from environment A to B illustrate peer-to-peer connections, therefore require ports to exports.

In UVM, transactions extend from the uvm\_sequence\_item class. Transactions contain all the information to model a communication in the environment. Besides the information, other methods can be defined in order to to operate at the transaction level.

The connect\_phase method connects the driver to the sequencer via TLM, where the driver's seq\_item\_port is connected to the sequencer's seq\_item\_export. This is shown in Figure 3.8. Seq\_item\_port implements a get/pull which defines the scenario where control and data flow in the opposite directions (see Figure

Figure 3.7: Canonical diagram for TLM connections.

3.5 where the method calls for this connection are analized in detail). This is a peer-to-peer connection as driver and sequencer exist inside the agent.

OVM also provides a uvm\_analysis\_port which is a specialized TLM based class that contains a list of analysis exports that are connected to it. This acts as a broadcast feature as it implements the transaction in multiples components that are connected to it. In Figure 3.8, the monitor inside the agent implements a uvm\_analysys\_port push/put connection defining the scenario where data and control flow in the same direction. This is a child to parent connection as the agent is the parent component of the monitor. Analysis port multiple receivers' feature is also represented as a scoreboard and a subscriber component receive the broadcasted packet from the agent. Analysis\_ports do not require a receiver, and can be left unconnected.

Figure 3.8: TLM connections example inside an agent.

Figure 3.9 shows multiple monitors forwarding packets through an analysis\_port connected to a export/imp inside the scoreboard. The scoreboard is the final destination and consumes the transaction with a write function.

Figure 3.9: Monitor analysis port connection to scoreboard component.

# Implementation of UVM

#### **Contents**

| 4.1 | Reusable Universal Verification Components | 37 |

|-----|--------------------------------------------|----|

| 4.2 | Voltage regulators' UVM environment        | 40 |

| 4.3 | Digital core UVM environment               | 43 |

| 4.4 | Power management unit UVM environment      | 45 |

# 4.1 Reusable Universal Verification Components

First and foremost, reusable UVM environments are described. These will be building blocks of the IP's UVM environments. These environments are designed for reusability, aiming for validation automation. Testbenches are designed to implement a verification plan based on thoroughly stressing the DUT with directed and pseudo-random stimuli, following a set of crossed SV's coverpoints, with scoreboard validation.

All voltage regulators have an input and output voltage pin and require an input reference voltage and a dedicated input for sensing the output voltage for feedback purposes. They also possess an enable input and digital inputs to control the output voltage. They also possess a digital interface responsible for control and configuration of the IP and an analog interface responsible for providing the current and voltage references and controlling the output voltage. As these interfaces are common to the majority of the regulators (LDOs, DCDC or switch-capacitor based) it is possible to create a parameterized reusable UVM environment, that runs a pre-defined set of tests to validate their correct implementation with respect to each regulator. Power and output interfaces also possess ports that exist in all regulators making it possible to generalize a UVM environment for each.

#### 4.1.1 Digital UVC

Voltage regulators have a digital interface ports that are grouped into a generic digital UVC. Table 4.1 shows the digital interface signals of the components of the PMU.

| Digital UVC | LDO      | СР      | Digital core |

|-------------|----------|---------|--------------|

| dis         | enzdvdd  | disdvdd | dis          |

| dissink     | dissink  | dissink | dissink      |

| dislvl      | dislvl   | dislvl  | -            |

| dislvlz     | dislvlz  | dislvlz | -            |

| vprog1      | di       | mode    | vprog1       |

| test        | test     | test    | test         |

| vprog2      | fastboot | swilim  | vprog2       |

| vprog3      | iomread  | -       | vprog3       |

| vprog4      | vfbread  | -       | vprog4       |

| vprog5      | iomsw    | dttrim  | vprog5       |

Table 4.1: Common digital interface signals

A digital UVC is generalized and encapsulated with default test sequences for each variable (Annex A.3 shows the implementation of this UVC). The agent inside this UVC can be set to active, driving stimuli to the DUT, or passive only acting as a listener of an interface. The passive implementation will be useful when testing the PMU digital core as this UVC can be replicated to sample the output of the registers for each regulator.

The sequence-item component possesses the following signals:

- dis The dis pin is used to enable and disbable the regulator.

- dislvl dislvl disables level converters and forces the regulator to ignore all driven digital signals

and assume default values. It is used to disable the interface core when digital supply is not present

or before the release of power-on-reset by the APC.

- dissink When held high it disables the sink resistors that perform a pull down of the output voltage,

if the core is disabled.

- vprog<sub>n</sub> The vprog<sub>n</sub> bits are connected to interface bits to program certain features of the regulator.

For example, vprog can be used to define the output voltage, to perform current or voltage trimming or to define operating modes of a regulator.

- test The test interface represent control pins used to force testing modes for characterization and production test. Test modes can provide controllability and observability of internal signals through the anatestbus output pin.

Specific LDO ports are described below.

- fastboot The fastboot pin acts on the start-up time of the regulator. When set to high it doubles the start voltage slope to reduce the start-up time.

- iomread and vfbread When set to high, the output load internal current mirrors and the output voltage dividers are activated. The mirrored current and divided voltage can be read from the iatb and vatb output pins, respectively.

- iomsw iomsw acts as a ratio selector for the load current mirror.

- di di acts as a 4 bit voltage programmer. It defines the output voltage of the regulator.

Specific CP ports are described below.

- dttrim The dttrim pin acts on the dead time between the switching phases of the regulator.

- *swilim swilim* programs the current limitation on the CP switches. Input and output current limitations are closely related to switch current limitation.

- mode mode controls the modes of operation of the CP.

To coordinate tests, functional test sequences are developed for each regulator.

Constraints are also set inside the sequence-item class, and enables CDV for a more thorough verification. These can be called from all environments that possess a digital UVC in a plug and play fashion.

#### 4.1.2 Power UVC

Similarly to the digital interface, all regulators have a power interface that is generalized to a generic power UVC. The agent inside this UVC is set to active as it provides supply voltages for the regulators. Different sequence-item classes are generated for each regulator and can be selected on higher levels of the test environment. By taking advantage of UVM object oriented features, the user can perform constraint layering, which allows the definition of new constraints for voltage margins and other parameters. Annex A.4 shows the implementation of this UVC.

Generic power interface sequence-item signals:

- vref Reference voltage.

- avdd Supply for analog circuits referenced to agnd.

- vcasn Supply for analog circuits referenced to agnd.

- dvdd Supply for the digital cells and level converters.

- *ibp1u0* Bias current for internal current mirrors.

- agnd, dgnd Analog and digital ground supply.

#### 4.1.3 Regulator UVC

All voltage regulators have an output interface that is also generalized and encapsulated inside a regulator UVC. This UVC is used for the validation of voltage regulator and digital core (see table 4.2).

Table 4.2: Common output interface signals

| Regulator UVC | LDO        | CP         | Digital core |

|---------------|------------|------------|--------------|

| VO            | vo         | VO         | VO           |

| pg            | pg         | pg         | pg           |

| pgdvdd        | pgdvdd     | pgdvdd     | pgdvdd       |

| anatestbus    | anatestbus | anatestbus | anatestbus   |

| anatestreq    | anatestreq | anatestreq | anatestreq   |

| rl_vprog1     | iatb       | cp1        | rl_vprog1    |

| rl_vprog2     | vatb       | cn1        | rl_vprog2    |

| rl_vprog3     | -          | cp2        | rl_vprog3    |

| rl_vprog4     | -          | cn2        | rl_vprog4    |

The correspondent agent is configured as active in the first case, and set to passive in the latter where test sequences are generated. The sequence-item component possesses the following signals:

• vo - Regulated output voltage.

- pg Power good indicator. It is set to high when the output voltage reaches 95% of the programmed voltage.

- pgdvdd pg converted to digital domain.

- anatestbus Output test bus.

- · anatestreq Output bit that is held high in test modes.

- rl\_vprog<sub>n</sub> Adaptable output real signal.

Specific LDO ports are described below.

- · iatb Output for internal current mirrors.

- · vatb Output for internal voltage dividers.

Specific CP ports are described below.

- cp1 Flying capacitor positive pin.

- cn1 Flying capacitor negative pin.

# 4.2 Voltage regulators' UVM environment

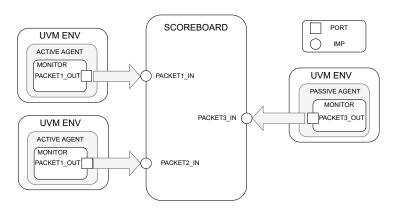

The proposed architecture for a generic voltage regulator UVM environment is displayed in Figure 4.1. This environment will be used to validate the CP and the LDO.

To provide reusability, separate UVM environments to test the digital and power ports are designed and encapsulated. These can be instantiated in other UVM voltage regulator environments. Alongside these environments, a configuration environment is also considered to generate and drive specific ports, define load variables and other parameters.

The testbench has four agents, one for each environment. The agents inside the power, configuration and digital environment are set to active and drive transactions to the DUT. The agent inside the regulator environment is set to passive and only samples the output interface of the DUT.

A virtual sequencer coordinates the generation of the constrained random stimuli for the sequencers on the active agents.

During run\_phase, input packets are driven to the DUT and the output port is sampled for each bundle of input signals. Each combination of input and corespondent output are orderly saved locally in queues as these will later be used to generate a reference model for comparison purposes.

Analog signals, inside the power UVC (see Annex A.4.2) are declared as 32 bit integers, as UVM does not support randomization of real values. These generated integer values are henceforth converted into a 64 bit floating point number to fit the model's real signal representation.

Figure 4.1: UVM environment for voltage regulator testing.

Annex A.1 show the top modules for UVM configuration and Annex A.1.2 defines the top module where the DUT and interface for each UVCs are instantiated. Annex A.2 depict the testbench UVM environment shown in figure 4.1. UVCs are declared alongside a virtual sequencer and a scoreboard component. As stated, digital and power UVCs are shown in Annexes A.3 and A.4 and run-phase calls to interface task for monitor and driver are represented. These interface calls implementation are shown in the interface source code (Annex A.6.1). The CP and LDO digital, power and output interface are shown in sections 4.1.1, 4.1.2 and 4.1.3.

#### 4.2.1 Sequence description

For each voltage regulator, test sequences are encapsulated inside the sequences class. These sequences aim for functional verification of the voltage regulator model. Therefore directed test are considered and described for active UVCs. The digital UVC defines control signals that control the voltage regulator. The validation process results in exercising all relevant input combinations of these control bits and verify if the DUT responds accordingly. Amongst these directed oriented stimuli, pseudorandom sequences are also defined. These are only limited by the constraints explicitly defined inside the sequence-item class.

For the LDO and CP, there are independent test sequences to enable and disable the regulator, sweeps of variables such as the *test* selector bus and *di* for output voltage regulation. Once these sequences are defined, the virtual sequencer on the top level of the environment (see Figure 3.4) is

programmed to coordinate generation of stimuli for all UVC's.

This level of granularity allows the user to create complex test scenarios focusing on functional verification with directed tests, fully pseudo-random scenarios or a combination of both.

#### 4.2.2 Scoreboards and reference models

During the check and report phases, validation metrics are generated from the UVM test environment. These contain information regarding simulation status, unmatched comparisons, coverage collection and detailed information about the test execution.