## UNIVERSIDADE DE LISBOA INSTITUTO SUPERIOR TÉCNICO

## GHEVC: An Efficient HEVC Decoder for Graphics Processing Units

Diego Felix de Souza

Supervisor: Doctor Leonel Augusto Pires Seabra de Sousa

Co-supervisor: Doctor Nuno Filipe Valentim Roma

Thesis approved in public session to obtain the PhD Degree in Electrical and Computer Engineering

**Jury final classification: Pass with Distinction**

### UNIVERSIDADE DE LISBOA INSTITUTO SUPERIOR TÉCNICO

## GHEVC: An Efficient HEVC Decoder for Graphics Processing Units

#### Diego Felix de Souza

Supervisor: Doctor Leonel Augusto Pires Seabra de Sousa

Co-supervisor: Doctor Nuno Filipe Valentim Roma

Thesis approved in public session to obtain the PhD Degree in Electrical and Computer Engineering

Jury final classification: Pass with Distinction

#### Jury

**Chairperson:** Doctor Isabel Maria Martins Trancoso, Instituto Superior Técnico da Universidade de Lisboa

#### **Members of the Committee:**

Doctor Sérgio Manuel Maciel de Faria, Escola Superior de Tecnologia e Gestão do Instituto Politécnico de Leiria

Doctor Gabriel Falcão Paiva Fernandes, Faculdade de Ciências e Tecnologia da Universidade de Coimbra

Doctor Maria Paula dos Santos Queluz Rodrigues, Instituto Superior Técnico da Universidade de Lisboa

Doctor David Manuel Martins de Matos, Instituto Superior Técnico da Universidade de Lisboa

Doctor Nuno Filipe Valentim Roma, Instituto Superior Técnico da Universidade de Lisboa

#### **Funding Institutions**

Fundação para a Ciência e a Tecnologia (FCT) Ph.D. scholarship SFRH/BD/76285/2011

## **Acknowledgments**

I wish to express my deep and sincere gratitude for all the support that I have received from my family. Their patience, love, and care were essential to the development of this Thesis. Also, I could not forget all the friends that I have made over these years that contributed to this work with inspiring discussions and fruitful collaboration. A special thanks to Kenan Turbić, Diogo Mera, Nuno Neves, José Germano, Lídia Kuan, Svetislav Momcilović, Jelena Milošević, Frederico Pratas, Mauricio Ramalho, Vladimir Ivannikov, Pham Tien Cuong, Sanchit Singh, Janine Iser, Dhiraj Shah, Berner Panti, Diego Batista, Daniel Albuquerque, Bruno Almeida, Bernardo Pereira, Antônio Neto, Felipe Soares, Otto Soares, Rodrigo Ferreira, Francisco Seixas, Luís Lucas, Danillo Graziosi, João Silva and Nerminko Omanić. I would like to name you all, but unfortunately, I have insufficient space for all of you. I also want to mention namely our Signal Processing Systems (SiPS) group, in particular, Professor Pedro Tomás and Ana Jesus. I would like to thank the Instituto de Engenharia de Sistemas e Computadores - Investigação e Desenvolvimento (INESC-ID) Lisboa and all the Departamento de Engenharia Electrotécnica e de Computadores from the Instituto Superior Técnico. My gratitude goes also to Spin Digital Video Technologies team for all the support. I would like to acknowledge the Fundação para a Ciência e a Tecnologia (FCT) for the financial assistance with the Ph.D. scholarship SFRH/BD/76285/2011. Special thanks go to Professor Aleksandar Ilić, his contribution was crucial for my work and personal growth, whom I have deeply displeased due to my behavior. I hope one day he can forgive all my mistakes.

Finally, I would also like to thank Professor Leonel Sousa and Professor Nuno Roma for welcoming me into their research group in one of my worst moments in life and for their quidance.

## **Abstract**

The compression efficiency achieved with the High Efficiency Video Coding (HEVC) standard comes at the cost of a significant increase of the computational load at both the encoder and the decoder. When considering HEVC decoders, such an increased burden is a limiting factor to accomplish real-time, especially for high definition video sequences (e.g. Ultra HD 4K and beyond). On the other hand, modern Graphics Processor Units (GPUs) have evolved into programmable and powerful parallel accelerators, being able to deliver an execution performance that greatly exceeds the capabilities of multi-core Central Processing Units (CPUs). However, this performance is mostly attainable for compute-intensive applications, with significant amount of data parallelism and regular memory access patterns. Accordingly, fully exploiting the GPU capabilities for a set of diverse and computationally complex HEVC decoding procedures is far from being a trivial task. In this scenario, the presented research is focused on developing an efficient GPU-based HEVC decoder, denoted as GHEVC. Such a data-parallel GHEVC decoder integrates the whole decompression pipeline, where the several HEVC procedures are executed in a highly heterogeneous environment composed by a CPU and a GPU. The herein presented algorithms comprehensively exploit both coarse and fine-grained parallelization opportunities in an integrated perspective by re-designing the execution pattern of the involved HEVC procedures, while simultaneously coping with their inherent computational complexity and data dependencies. As a result, the proposed GHEVC decoder, which is fully compliant with the HEVC standard, has showed to be a remarkable approach, being capable of satisfying hard real-time requirements to process Ultra HD 4K video sequences.

## Keywords

Parallel Processing, Graphics Processor Units (GPUs), High Efficiency Video Coding (HEVC), Video Decoding, Real-time.

## Resumo

A eficiência de compressão alcançada pela norma High Efficiency Video Coding (HEVC) é conseguida à custa de um aumento significativo da carga computacional no codificador e no descodificador. Para descodificadores HEVC, o aumento da carga computacional é um fator limitativo para a execução em tempo real, especialmente para sequências de vídeo de alta definição (Ultra HD 4K). Por outro lado, as Unidades de Processamento Gráfico (GPUs) evoluíram significativamente ao longo dos últimos anos, sendo hoje poderosos aceleradores programáveis, capazes de atingir um nível de desempenho que excede em muito o de uma Unidade de Processamento Central (CPU) multinúcleo. No entanto, este nível de desempenho é, em geral, atingido para aplicações de computação intensiva, com um alto grau de paralelismo e acessos regulares à memória. Assim, a exploração efetiva das capacidades de processamento das GPUs para os procedimentos da norma HEVC, que são computacionalmente complexos, está longe de ser uma tarefa fácil. Neste cenário, o trabalho apresentado foca-se na investigação e desenvolvimento de um descodificador HEVC computacionalmente eficiente, baseado na utilização de GPUs, a que se designou de GHEVC. O descodificador GHEVC inclui todos os procedimentos do HEVC, sendo estes executados num sistema heterogéneo constituído por um CPU e uma GPU. Desta forma, os algoritmos aqui apresentados exploram oportunidades de paralelismo numa perspectiva integrada, através de uma nova execução dos procedimentos do descodificador HEVC, os quais lidam com as suas inerentes complexidades e dependências computacionais. Como resultado, o descodificador GHEVC, totalmente compatível com a norma HEVC, é capaz de satisfazer os rigorosos requisitos de tempo real para processar sequências de vídeo Ultra HD 4K.

#### **Palavras Chave**

Processamento Paralelo, Unidades de Processamento Gráfico (GPUs), High Efficiency Video Coding (HEVC), Descodificação de Vídeo, Tempo Real.

## **Contents**

| 1 | Intro | oductio | on                                            | 1  |

|---|-------|---------|-----------------------------------------------|----|

|   | 1.1   | Motiva  | ation                                         | 4  |

|   | 1.2   | Main (  | Objectives and Contributions                  | 4  |

|   | 1.3   | Outlin  | e                                             | 6  |

| 2 | Ove   | rview   | of Graphics Processing Units                  | 7  |

|   | 2.1   | Progra  | amming Model                                  | 9  |

|   |       | 2.1.1   | Host and Device Synchronization               | 10 |

|   |       | 2.1.2   | Threads Synchronization                       | 11 |

|   |       | 2.1.3   | Memory Fence Functions                        | 11 |

|   | 2.2   | Memo    | ry Hierarchy                                  | 12 |

|   |       | 2.2.1   | Host Memory                                   | 12 |

|   |       | 2.2.2   | Global Memory                                 | 12 |

|   |       | 2.2.3   | Constant Memory                               | 13 |

|   |       | 2.2.4   | Texture Memory                                | 13 |

|   |       | 2.2.5   | Local Memory                                  | 13 |

|   |       | 2.2.6   | Shared Memory                                 | 13 |

|   | 2.3   | Comp    | utational Architecture                        | 14 |

|   | 2.4   | CUDA    | Alternatives for Extended Portability: OpenCL | 16 |

|   | 2.5   | Summ    | nary                                          | 18 |

| 3 | Вас   | kgrour  | nd and State of the Art                       | 19 |

|   | 3.1   | Gener   | ral Overview of the HEVC Standard             | 20 |

|   |       | 3.1.1   | Entropy Decoder                               | 22 |

|   |       | 3.1.2   | De-quantization and Inverse Transform         | 23 |

|   |       | 3.1.3   | Motion Compensation                           | 26 |

|   |       | 3.1.4   | Intra Prediction                              | 29 |

|   |       | 3.1.5   | Deblocking Filter                             | 31 |

|   |       | 3.1.6   | Sample Adaptive Offset                        | 33 |

|   |       | 3.1.7   | Profiles, Tiers, and Levels                   | 35 |

#### Contents

|   | 3.2 | Complete HEVC Decoder Implementations         | 36 |

|---|-----|-----------------------------------------------|----|

|   |     | 3.2.1 CPU-based Implementations               | 36 |

|   |     | 3.2.2 Dedicated Architectures Implementations | 37 |

|   |     | 3.2.3 GPU-based Implementations               | 38 |

|   | 3.3 | Summary                                       | 39 |

| 4 | GHE | EVC Parallel Algorithms                       | 41 |

|   | 4.1 | Sequence-level and Frame-level Parallelism    | 42 |

|   | 4.2 | De-quantization and Inverse Transform         | 45 |

|   | 4.3 | Motion Compensation                           | 48 |

|   | 4.4 | Intra Prediction                              | 52 |

|   | 4.5 | Deblocking Filter                             | 56 |

|   | 4.6 | Sample Adaptive Offset                        | 58 |

|   | 4.7 | Summary                                       | 60 |

| 5 | Ехр | erimental Evaluation                          | 63 |

|   | 5.1 | Kernel-Level Thread Block Configuration       | 65 |

|   | 5.2 | GHEVC Profiling Analysis                      | 67 |

|   | 5.3 | CUDA Streams Scalability                      | 69 |

|   | 5.4 | Comparison with Previous Intra GHEVC          | 71 |

|   | 5.5 | GHEVC Decoding Performance                    | 73 |

|   | 5.6 | Summary                                       | 77 |

| 6 | Con | clusions and Future Work                      | 79 |

|   | 6 1 | Futuro Work                                   | 92 |

## **List of Figures**

| 2.1  | High level representation of CPU and GPU architectures                                       | 9  |

|------|----------------------------------------------------------------------------------------------|----|

| 2.2  | An example of a grid of ThBs                                                                 | 10 |

| 3.1  | Example of the CTU partitioning into CUs, PUs and TUs                                        | 20 |

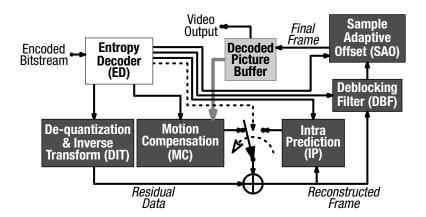

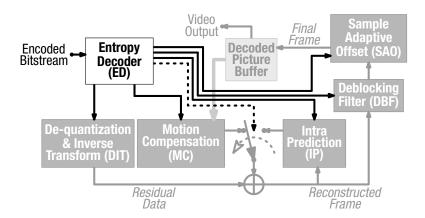

| 3.2  | Block diagram of an HEVC decoder                                                             | 21 |

| 3.3  | Block diagram of an HEVC decoder: entropy decoder                                            | 22 |

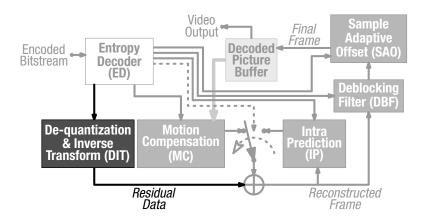

| 3.4  | Block diagram of an HEVC decoder: de-quantization and inverse transform                      | 24 |

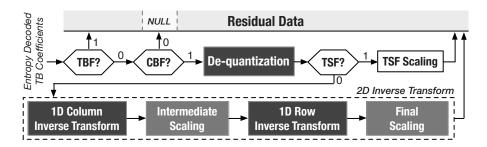

| 3.5  | The HEVC residual data decompressing flowchart                                               | 25 |

| 3.6  | Block diagram of an HEVC decoder: motion compensation                                        | 27 |

| 3.7  | PU partition modes for the HEVC inter prediction                                             | 27 |

| 3.8  | Luma sample positions at quarter-pel resolution and filtering features                       | 28 |

| 3.9  | Block diagram of an HEVC decoder: intra prediction                                           | 29 |

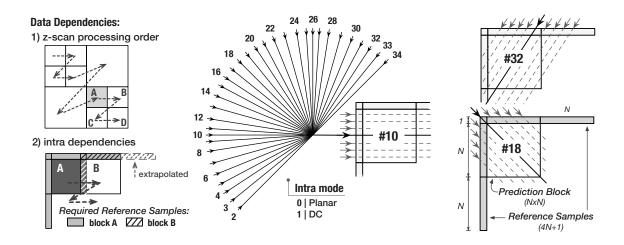

| 3.10 | Intra prediction dependencies and modes                                                      | 30 |

| 3.11 | Block diagram of an HEVC decoder: deblocking filter                                          | 32 |

| 3.12 | Deblocking Filter boundary and filtering types                                               | 33 |

| 3.13 | Block diagram of an HEVC decoder: sample adaptive offset                                     | 34 |

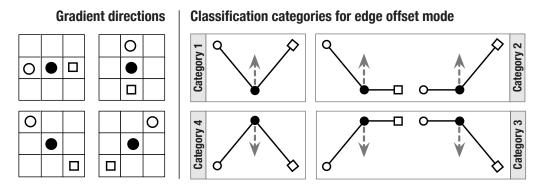

| 3.14 | SAO gradient directions and classification categories                                        | 34 |

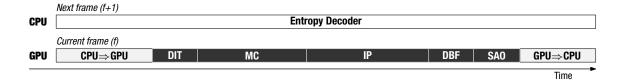

| 4.1  | Proposed CPU+GPU integration of the GHEVC decoder                                            | 43 |

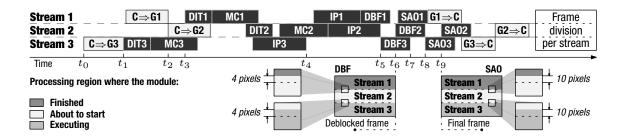

| 4.2  | Asynchronous CUDA Stream processing in the proposed GHEVC video decoder                      | 44 |

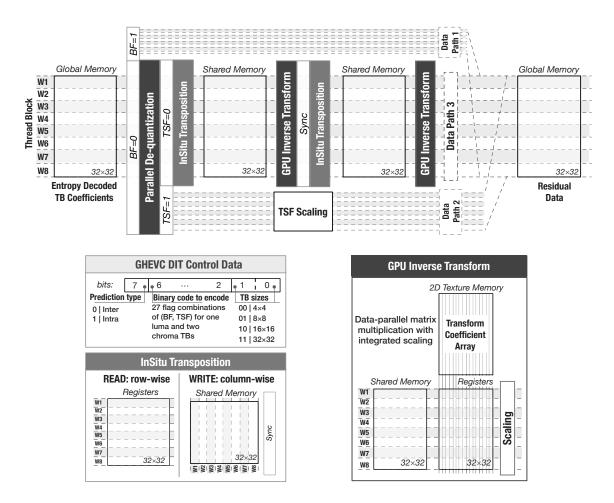

| 4.3  | Overall de-quantization and 2D inverse transform implementation in the GPU for               |    |

|      | one 32×32 luma TB                                                                            | 46 |

| 4.4  | Example of GHEVC DIT warp and ThB assignments                                                | 48 |

| 4.5  | Thread blocks/warps assignment and the proposed GPU Motion Compensation                      |    |

|      | functionality                                                                                | 50 |

| 4.6  | Flowchart and control data of the GHEVC MC module                                            | 51 |

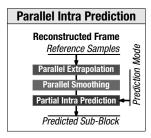

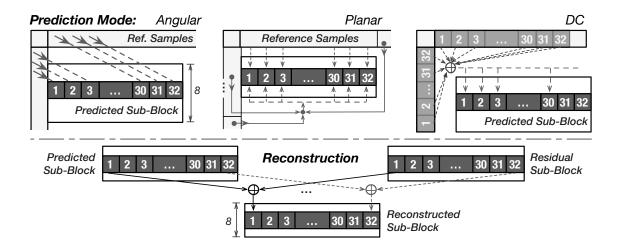

| 4.7  | Framework of the GHEVC IP module.                                                            | 54 |

| 4.8  | Proposed GHEVC Partial Intra Prediction design for the <i>Mode Prediction</i> and <i>Re-</i> |    |

|      | construction steps                                                                           | 55 |

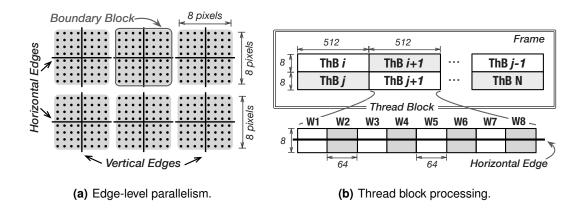

| 4.9  | Thread blocks/warps assignment of the GHEVC Deblocking Filter                                | 57 |

#### **List of Figures**

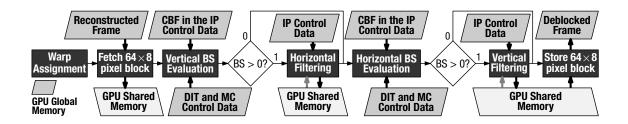

| 4.10 | Flowchart of the GHEVC DBF module (luma component)                                        | 58 |

|------|-------------------------------------------------------------------------------------------|----|

| 4.11 | Thread blocks/warps assignment of the proposed GHEVC SAO filtering                        | 59 |

| 4.12 | Flowchart and control data of the GHEVC SAO module (luma or chroma component). $ \\$      | 60 |

| 5.1  | Normalized frame processing time, considering QP=22 the reference, for <i>All Intra</i> , |    |

|      | Random Access and Low Delay configurations                                                | 68 |

| 5.2  | Evaluation of the performance scalability with the number of CUDA Streams for All         |    |

|      | Intra, Random Access and Low Delay configurations.                                        | 70 |

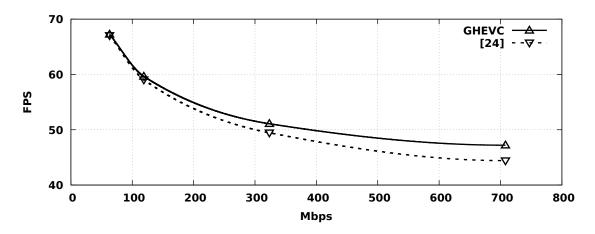

| 5.3  | Overall performance of the proposed GHEVC on the Titan GPU for All Intra configu-         |    |

|      | ration                                                                                    | 72 |

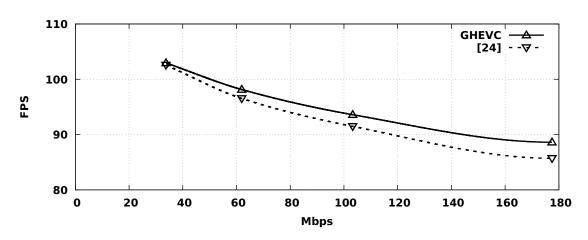

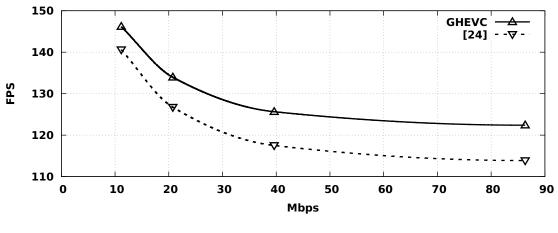

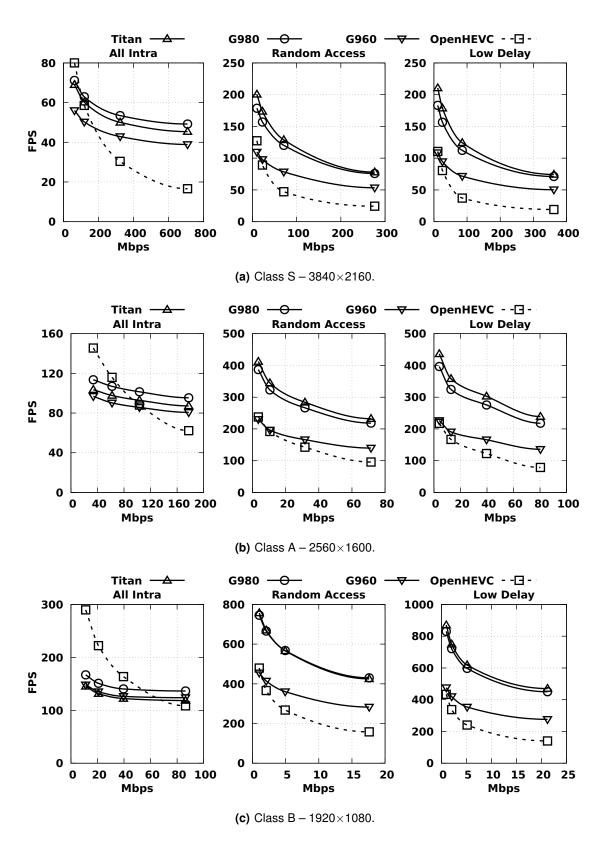

| 5.4  | Evaluation of the GHEVC decoder performance using NVIDIA Maxwell GPUs over                |    |

|      | the OpenHEVC decoder (running on the CPU)                                                 | 74 |

## **List of Tables**

| 2.1 | GPU technical specifications, according to their Compute Capability                | 16 |

|-----|------------------------------------------------------------------------------------|----|

| 2.2 | Device memory features summary                                                     | 17 |

| 2.3 | Comparison between the terminology used in CUDA and OpenCL                         | 17 |

| 3.1 | BS values for the luma boundary between two neighboring pixel blocks               | 32 |

| 3.2 | Tier and level limit examples for <i>Main</i> and <i>Main 10</i> profiles          | 36 |

| 5.1 | Selected setup and video sequences                                                 | 64 |

| 5.2 | Available NVIDIA GPU devices from Maxwell and Kepler architectures                 | 65 |

| 5.3 | GPU kernel execution time (in ms/frame) when varying the number of warps in a ThB. | 66 |

| 5.4 | Average performance (FPS) obtained per tested sequence with the proposed           |    |

|     | GHEVC decoder                                                                      | 76 |

## **List of Acronyms**

API Application Programming Interface

**BB** Boundary Block

**BF** Bypass Flag

**BS** Boundary filtering Strength

**CABAC** Context-Adaptive Binary Arithmetic Coding

CBF Coded Block Flag

CPU Central Processing Unit

CTU Coding Tree Unit

**CU** Coding Unit

**CUDA** Compute Unified Device Architecture

**DBF** Deblocking Filter

**DCT** Discrete Cosine Transform

**DIT** De-quantization and Inverse Transform

**DRAM** Dynamic Random-Access Memory

**DSP** Digital Signal Processor

**DST** Discrete Sine Transform

**DVFS** Dynamic Voltage Frequency Scaling

**FPGA** Field-Programmable Gate Array

FPS frames per second

GHEVC GPU-based HEVC

**GPU** Graphics Processing Unit

#### **List of Acronyms**

**HD** High Definition

**HEVC** High Efficiency Video Coding

HIP Heterogeneous-compute Interface for Portability

**HM** HEVC Test Model

**ILP** Instruction-level parallelism

IP Intra Prediction

**ISO/IEC** International Standardization Organization/International Electrotechnical Commission

ITU International Telecommunications Union

JCT-VC Joint Collaborative Team on Video Coding

Mbps megabit per second

MC Motion Compensation

MPEG Moving Picture Experts Group

**OpenCL** Open Computing Language

**OpenGL** Open Graphics Library

**OpenMP** Open Multi-Processing

**OWF** Overlapped Wavefront

**PB** Prediction Block

**PU** Prediction Unit

**QP** Quantization Parameter

RVC-CAL Reconfigurable Video Coding CAL Actor Language

**SAO** Sample Adaptive Offset

**SIMD** Single Instruction, Multiple Data

**SIMT** Single Instruction Multiple Thread

**SM** Streaming Multiprocessor

**SoC** System on Chip

**SVT** Sveriges Television AB

**ThB** Thread Block

**TB** Transform Block

**TBF** Transquant Bypass Flag

**TSF** Transform Skip Flag

**TU** Transform Unit

VCEG Video Coding Experts Group

**VoD** Video on Demand

WPP Wavefront Parallel Processing

## Introduction

#### Contents

| 1.1 | Motivation                        | 4 |

|-----|-----------------------------------|---|

| 1.2 | Main Objectives and Contributions | 4 |

| 1.3 | Outline                           | 6 |

In 2015, digital video transfers were reported to be responsible for around 70% of the total global internet traffic [1]. In general, those video sequences correspond to: Internet video (e.g., YouTube¹ and Hulu²); live Internet video; Internet video to TV (e.g., Netflix³); online video purchases and rentals; video conference; and web-based video monitoring. Although the supply of good quality video contents is still low, the demand for High Definition (HD) videos is extremely large, which includes video resolutions such as Full HD (1920×1080 pixels) and beyond (Ultra HD). In fact, Ultra HD video sequences are expected to be 20.7% of all Video on Demand (VoD) traffic in 2020 [1], when considering Ultra HD 4K (3840×2160 pixels) and Ultra HD 8K (7680×4320 pixels) resolutions. This demand for higher video resolutions in applications and services has led to a consequent growth for bandwidth and storage requirements, which results in greater demands for higher video compression rates and more advanced video coding mechanisms.

In order to satisfy these needs, the Joint Collaborative Team on Video Coding (JCT-VC) [2] was created in 2010 to develop a new standard. Such consortium integrated several video coding experts from: *i*) International Telecommunications Union (ITU)-Telecommunication Standardization Sector Study Group 16 Video Coding Experts Group (VCEG); and *ii*) International Standardization Organization/International Electrotechnical Commission (ISO/IEC) JTC 1/SC 29/WG 11 Moving Picture Experts Group (MPEG). The requirements of this new video standard were defined and the corresponding joint call for proposals was published in the same year [3]. In 2013, the first version of the new video standard [4], designated as High Efficiency Video Coding (HEVC), was released, particularly focused on two key issues: increase the video resolution and allow parallel processing [5]. By relying on cutting-edge encoding techniques, the newest video coding standard has shown to reduce approximately by half the bitrate required to compress a video sequence with the same visual quality [6, 7], when compared to its predecessor H.264/MPEG-4 AVC standard [8] with High profile [9], which was one of the most applied video coding standards in 2013.

As a result, the HEVC standard does not only provide a more efficient utilization of the storage resources, but it also offers a higher suitability to Ultra HD 4K and Ultra HD 8K video resolutions, which are seen as near-future targets for video services. Despite its higher compression efficiency in comparison with the H.264/MPEG-4 AVC standard, the computational complexity of optimized HEVC and H.264/MPEG-4 AVC decoders are not significantly different [10, 11] (no more than 2× slower). Nevertheless, the decoding procedures of Ultra HD video sequences greatly increase the computational load of HEVC decoders, mainly due to the larger amount of data to be processed when compared with more modest video resolutions. In this way, to achieve real-time capabilities for Ultra HD video sequences in HEVC decoders, it is highly required to exploit the available parallelism either in hardware or in software [12]. In particular, HEVC decoders implementations can take advantage of multi- or many-core architectures by employing all the parallelization models

<sup>&</sup>lt;sup>1</sup>[Online] Available: https://www.youtube.com

<sup>&</sup>lt;sup>2</sup>[Online] Available: http://www.hulu.com <sup>3</sup>[Online] Available: https://www.netflix.com

that are made available by the HEVC standard [13, 14], which are categorized in:

- **Sequence-level parallelization**: processes several pictures at the same time, provided that their temporal dependencies are satisfied.

- **Picture-level parallelization**: simultaneously decodes independent parts of the picture, where the number and size of these independent parts are set on the encoder side.

- Block-level parallelization: decompresses non-overlapping procedures or parts of a pixel block, where a pipeline scheme is elaborated for different decoding procedures; or nonoverlapping parts of the pixel block for the same decoding procedure are processed in parallel.

Each of these models provides different levels of parallelism, which can be exploited to increase the performance of hardware HEVC decoders [15], as well as software-based decoders for multi-or many-core Central Processing Units (CPUs) [16]. Nonetheless, each chosen architecture and parallelization model has its own advantages and limitations.

When considering the limitations of the encoder side, a set of HEVC features and parameters (e.g., motion vectors, block partitioning and quantization step) can be carefully selected and configured to achieve the best trade off between distortion, compression rate and computational complexity [17]. However, high compression rates are only attained at the cost of a corresponding high computational load, since the encoded bitstream is usually generated by taking advantage of the main HEVC compression features, such as: i) several partitioning modes, including asymmetric partitioning to adapt to the video content; ii) 35 intra prediction modes allied with quarter-pel motion vectors and interpolation filters, to exploit spatial and temporal correlation; iii) different transform types and block sizes (from  $32 \times 32$  to  $4 \times 4$ ) to reduce the residual data redundancy; and iv) in-loop filtering, to remove block artifacts and sample distortion. Furthermore, although the encoder may select the coding tools which it considers to be most suitable, an HEVC decoder has to be able to decompress any compliant bitstream, for the defined set of profiles, levels and tiers [18], regardless of the involved computational complexity.

Hence, the specified profile, level and tier of an HEVC decoder shall indicate the available processing capabilities to decode a bitstream. In particular, a set of coding tools that may be used to encode a video sequence into a bitstream is defined by the profile. The level and tier, among other settings, limit the maximum picture size, the picture buffer sizes, and the bit rates. Therefore, designing a decoder with the ability to comply not only with the computationally complex HEVC operations, but also with the strict frame rate requirements, is far from being a trivial task.

#### 1.1 Motivation

Hardware-based HEVC decoder implementations usually target specific profiles, levels and tiers, in order to achieve low power consumption. Nevertheless, their decoding capabilities are often limited to a few frame resolutions and rates. Moreover, hardware-based HEVC decoders are not present in all computing devices, where they are mostly found in System on Chips (SoCs) for embedded and mobile devices (e.g., Qualcomm Snapdragon 820<sup>4</sup>). When considering laptop and desktop devices, hardware-based HEVC decoders are also included in the latest processors (e.g., Intel Skylake<sup>5</sup>). A remarkable drawback of hardware accelerated decoders is to take up valuable die space on a SoC. Furthermore, hardware-based decoders can't be redesigned after production, while reconfigurable hardware, e.g., Field-Programmable Gate Array (FPGA), despite being more flexible, lead to higher power consumption when compared to dedicated hardware acceleration.

On the other hand, software-based HEVC decoders are not limited by specific profiles, levels and tiers. However, software approaches are usually limited by the architecture capabilities and the amount of parallelism exposed by the algorithm. Usually, software-based HEVC decoders take only advantage of the CPU and they often exploit Single Instruction, Multiple Data (SIMD) instruction sets [16], as well as multithreading [19]. By only exploiting the CPU, most software decoders do not employ the full capabilities of current computing devices, which are often composed by heterogeneous systems, consisting of a CPU and a Graphics Processing Unit (GPU).

In the past decade, GPUs have evolved from a fixed-function graphics pipeline to a programmable and general purpose parallel processor, with the offered computing power often exceeding the processing capabilities of multi-core CPUs [20]. Nevertheless, while the CPU is predominantly designed and optimized for sequential code performance, the GPU is specialized for compute-intensive and highly parallel data-level computation [21], like 3D rendering. Hence, the GPU has been designed for intense data processing, rather than data caching and control flow. In what concerns the processing acceleration, modern GPUs can achieve performance levels that greatly exceed the capabilities of multi-core CPUs [21].

#### 1.2 Main Objectives and Contributions

Although GPUs have evolved to programmable and powerful parallel accelerators, they are mostly suitable for compute-intensive applications with a high parallelism degree. In this way, to fully exploit the GPU architecture, the targeted application has to be conveniently redesigned, in order to maximize the degree of parallelism and to take advantage of the GPU memory hierarchy and high execution concurrency. As a result, fully exploiting the GPU capabilities for a set of diverse and computationally complex HEVC decoding procedures is usually a difficult task.

<sup>&</sup>lt;sup>4</sup>[Online] Available: https://www.qualcomm.com/products/snapdragon/processors/820

<sup>&</sup>lt;sup>5</sup>[Online] Available: https://software.intel.com/en-us/blogs/2015/12/11/codecs-are-they-slowing-you-down

Hence, the main objective of this Thesis is the investigation of a comprehensive GPU-based HEVC (GHEVC) decoder, which will ensure a fully compliant and real-time HEVC decoding for Ultra HD video sequences, by offloading most of the HEVC procedures to the GPU. The main contributions of this Thesis are summarized as follows.

- A comprehensive redesign of all HEVC decoder procedures, in order to decode a video sequence in GPU accelerators, which implies a fully exploitation of the available parallelism, optimization of the memory access and increase of the instruction throughput.

- A unified design of all the GHEVC components, by reinforcing data sharing among different HEVC procedures by taking advantage of the GPU's memory hierarchy.

- A frame-level GPU parallel processing scheme, where different parts of the frame are processed in parallel, while ensuring the HEVC standard compliance.

With these goals in mind, it can be identified the set of contributions presented in this Thesis, which already led to the following publications in international journals and conferences:

#### Journals

- [22]: D. F. de Souza, A. Ilic, N. Roma, and L. Sousa. GHEVC: An efficient HEVC decoder for graphics processing units. *IEEE Transactions on Multimedia*, 19(3):459–474, Mar. 2017. ISSN 1520-9210. doi:10.1109/TMM.2016.2625261.

- [23]: B. Wang, M. Alvarez-Mesa, C. C. Chi, B. Juurlink, D. F. de Souza, A. Ilic, N. Roma, and L. Sousa. GPU parallelization of HEVC in-loop filters. *International Journal of Parallel Programming*, pages 1–21, 2017. ISSN 1573-7640. doi:10.1007/s10766-017-0488-z.

- [24]: D. F. de Souza, A. Ilic, N. Roma, and L. Sousa. GPU-assisted HEVC intra decoder. *Journal of Real-Time Image Processing*, 12(2):531–547, 2016. ISSN 1861-8219. doi:10.1007/s11554-015-0519-1.

#### Conferences

- [25]: B. Wang, M. Alvarez-Mesa, C. C. Chi, B. Juurlink, D. F. de Souza, A. Ilic, N. Roma, and L. Sousa. Efficient HEVC decoder for heterogeneous CPU with GPU systems. In 2016 IEEE 18th International Workshop on Multimedia Signal Processing (MMSP), pages 1–6, Sept. 2016. doi:10.1109/MMSP.2016.7813353.

- [26]: D. F. de Souza, A. Ilic, N. Roma, and L. Sousa. GPU acceleration of the HEVC decoder inter prediction module. In 2015 IEEE Global Conference on Signal and Information Processing (GlobalSIP), pages 1245–1249, Dec. 2015. doi:10.1109/GlobalS IP.2015.7418397.

- [27]: D. F. de Souza, A. Ilic, N. Roma, and L. Sousa. HEVC in-loop filters GPU parallelization in embedded systems. In *Embedded Computer Systems: Architectures, Modeling, and Simulation (SAMOS), 2015 International Conference on*, pages 123–130, July 2015. doi:10.1109/SAMOS.2015.7363667.

- [28]: D. F. de Souza, A. Ilic, N. Roma, and L. Sousa. Towards GPU HEVC intra decoding: Seizing fine-grain parallelism. In 2015 IEEE International Conference on Multimedia and Expo (ICME), pages 1–6, June 2015. doi:10.1109/ICME.2015.7177515.

- [29]: D. F. de Souza, N. Roma, and L. Sousa. OpenCL parallelization of the HEVC de-quantization and inverse transform for heterogeneous platforms. In 22nd European Signal Processing Conference (EUSIPCO), pages 755–759, Sept. 2014.

- [30]: D. F. de Souza, N. Roma, and L. Sousa. Cooperative CPU+GPU deblocking filter parallelization for high performance HEVC video codecs. In 2014 IEEE International Conference on Acoustics, Speech and Signal Processing (ICASSP), pages 4993–4997, May 2014. doi:10.1109/ICASSP.2014.6854552.

#### Accepted ()under production)

[31]: B. Wang, D. F. de Souza, M. Alvarez-Mesa, C. C. Chi, B. Juurlink, A. Ilic, N. Roma, and L. Sousa. Highly parallel HEVC decoding for heterogeneous systems with CPU and GPU. Signal Processing: Image Communication, 2018.

#### 1.3 Outline

This dissertation is organized in five chapters, according to the following outline.

- Chapter 2: introduces the basic principles of the GPU architecture and programming, as well as a brief overview of the memory hierarchy and optimization techniques.

- Chapter 3: provides an overview of the functional principles behind the HEVC standard, as well as a review of the state-of-the-art parallel HEVC procedures and decoder implementations.

- Chapter 4: presents a detailed description of the proposed approach for the parallelization

of the HEVC decoder, which was denoted GHEVC. GHEVC modules integration are also

comprehensively presented, which includes the chosen frame-level parallel processing.

- Chapter 5: discusses the profiling and evaluation of the implemented GHEVC decoder, where the obtained experimental results are presented and discussed for each individual module.

- Chapter 6: draws the main conclusions of this Thesis and the final remarks for future work.

#

## Overview of Graphics Processing Units

| 2.1 | Programming Model                                  |

|-----|----------------------------------------------------|

| 2.2 | Memory Hierarchy                                   |

| 2.3 | Computational Architecture                         |

| 2.4 | CUDA Alternatives for Extended Portability: OpenCL |

| 2.5 | Summary                                            |

Along the past years, multi-core heterogeneous systems have proven to be able to offer more performance or energy efficiency than the homogeneous multi-core counterparts. When considering heterogeneous systems consisting of CPU and GPU devices, it has been shown that further computational gains can be achieved when the best features of both devices are exploited cooperatively [32]. Since the goal of this research is to accelerate all possible HEVC procedures by exploiting GPU devices, the GPU main characteristics and capabilities are comprehensively discussed in this chapter.

In 1999, the NVIDIA GeForce 256 GPU [33] was made available in the market. Contrasting to the former graphics cards, the NVIDIA GeForce 256 GPU was the first to include a single-chip 3D real-time graphics processor with a configurable 32-bit floating-point vertex transform and lighting processor, which were programmed through Application Programming Interfaces (APIs), such as Open Graphics Library (OpenGL) and Microsoft DirectX 7 (DX7).

As programmable GPU cores evolved, GPUs became more flexible and easy to program. Nevertheless, those GPUs were mainly developed for graphics processing purposes, meaning that they were very difficult to use because programmers had to use the equivalent of graphics APIs, such as OpenGL, to access the GPU cores. For example, the work in [34] addresses the overflow and rounding problems in video decoding interpolation, implemented by a pipeline of vertex/pixel shader procedures. In [35], a stream-based computing model was proposed in order to incorporate GPUs into GRID environment and use them to replace CPUs as the main computing devices.

In November 2006, NVIDIA released the Compute Unified Device Architecture (CUDA) [36], which included several new features to facilitate general-purpose computing on GPUs. On the other hand, in 2009, the Open Computing Language (OpenCL) [37] framework arose as a highly viable alternative to exploit task-parallelism and data-parallelism across multiple heterogeneous devices, including both CPUs and GPUs. Although OpenCL offers code portability among different GPU manufacturers, only with CUDA it is possible to fully exploit the capabilities of current NVIDIA GPU architectures and to ensure a fine-grain control over program executions. In particular, although the tested NVIDIA devices (presented in Chapter 5) fully support the OpenCL version 1.2 API [38], some of the CUDA functions and configurations are not supported in this OpenCL specification. Nevertheless, although CUDA terminology shall be extensively adopted in this dissertation, the provided explanations regarding the main functional principles and parallelization strategies for the proposed GHEVC decoder are oblivious to the programming model. In fact, since the OpenCL specification largely relies on the NVIDIA CUDA legacy, the proposed approaches can be easily ported to the OpenCL API with only slight modifications.

Regardless the considered framework (CUDA or OpenCL), it is important to notice that while the CPU is conceived and optimized to exploit Instruction-level parallelism (ILP) or sequential application performance, the GPU device is designed for applications with a specific set of characteristics [39], such as: high computational requirements, high level of data parallelism and

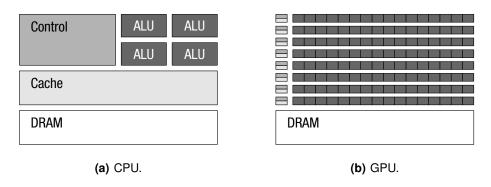

Figure 2.1: High level representation of CPU and GPU architectures.

prioritizing throughput over latency. In this way, the GPU architecture devotes more transistors to data processing rather than data caching and control flow [36], as it is represented in Figure 2.1, which depicts a simplified representation of both architectures. Hence, the same program (denoted as *kernel* in GPU terminology) is executed on many data elements in parallel, where there is a lower requirement for advanced flow control. Also, since the computational requirements are large, the memory access latency can be hidden with calculations instead of relying on large caches. Hence, the higher the level of data parallelism and computational load, the better the GPU performance over the CPU's.

#### 2.1 Programming Model

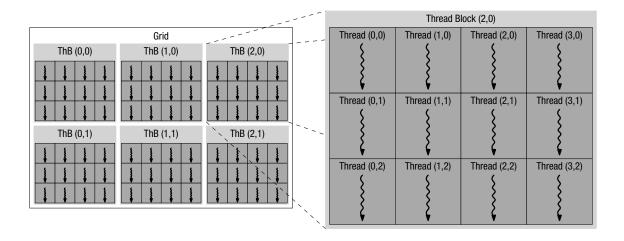

The GPU programming model is designed to run the same program (kernel) across hundreds or thousands of concurrent threads and cores [40]. Hence, a CUDA application is organized into a host<sup>1</sup> program, consisting of one or more sequential threads running on the host CPU, and one or more parallel kernels that are conveniently described for execution on the parallel processing device (GPU). To achieve this parallel processing capability, each kernel defines a multidimensional grid of thread blocks according to its application/algorithm requirements. The threads in a Thread Block (ThB) are also organized in a multidimensional way, where each thread as a unique index. This provides a natural way to invoke computation across the elements in a regular domain, such as a vector or a matrix [36].

The threads in a ThB are assumed to be executed in the same processor and to share memory resources. However, since the processor resources are limited, there is a limit for the number of threads in a ThB. In current GPUs, a ThB may contain up to 1024 threads. However, a kernel can be executed by multiple equally-shaped ThB, so that the total number of threads is equal to the number of threads per ThB times the number of ThBs in a grid [36].

Although the threads inside a ThB can interact and cooperate among themselves through

<sup>&</sup>lt;sup>1</sup>For the sake of clarity, in the remaining of this Thesis the CPU is denoted as the *host*, whereas the GPU is denoted as the *device*.

Figure 2.2: An example of a grid of ThBs.

barrier synchronization and shared access to a ThB private memory space, the ThBs are required to be executed independently of the other ThBs [41]. This means that it must be possible to execute them in any order, in parallel or in series. This independence requirement allows ThBs to be scheduled in any order across any number of cores, making the programming model scalable across an arbitrary number of cores, as well as across a variety of parallel architectures. For example, Figure 2.2 presents a kernel grid with 6 ThBs, where each ThB has 12 threads. If a GPU processor can handle only one ThB at a time, the same kernel would run up to  $6 \times$  faster in a GPU with 6 processors than on a GPU with just one, without any kernel modification by the programmer.

#### 2.1.1 Host and Device Synchronization

According to the CUDA programming model, the kernel (computation) and memory transfers (host to device and device to host) are organized in *streams* [36]. A stream is a sequence of commands (kernels and memory transfers) that are executed in order. On the other hand, streams may execute concurrently or out of order with respect to each other (according to the device resources and capabilities). In this way, concurrent operations, such as overlapped kernels and memory transfers are achieved with multiple streams.

The kernels are always issued asynchronously, which means that the host thread does not wait until a kernel finishes its execution. On the other hand, the memory transfers between host and device may be synchronous or asynchronous.

The programming model also defines explicit and implicit barrier synchronizations between the host and the device. Explicit synchronizations include barriers (among others): *i*) at device-level (*cudaDeviceSynchronize*), for which the host thread waits until all preceding commands in all streams of all host threads have completed; and *ii*) at stream-level (*cudaStreamSynchronize*), for which the host thread waits until all preceding commands in the given stream have completed, while allowing other streams to continue executing on the device.

#### 2.1.2 Threads Synchronization

The threads of a single thread block are allowed to synchronize with each other via barrier synchronizations (e.g. \_\_syncthreads). Hence, as soon as the device thread reaches one of these barriers, it waits until all threads in the ThB have reached that point and all memory accesses have been made by these threads prior to the barrier is visible to all threads in the ThB. Thus, inter-ThB barrier synchronization is used to coordinate communication between the threads of the same ThB. For example, when some device threads within a ThB access the same addresses in the device's memory, there are potential read-after-write, write-after-read, or write-after-write hazards. These data hazards can be avoided by synchronizing threads in-between these accesses.

#### 2.1.3 Memory Fence Functions

The programming model described here assumes a device with a weakly-ordered memory model, which means: *i*) the order in which a device thread writes data to the device or host memory is not necessarily the order in which the data is observed as being written by another device or host thread; and *ii*) the order in which a device thread reads data from the device or host memory is not necessarily the order in which the read instructions appear in the program for instructions that are independent to each other. To solve this problem, memory fence functions can be used to enforce some ordering, when threads consume some data produced by other threads in the same kernel.

In the CUDA programming model, three memory fence functions are available [36] (according to the device capabilities):

- \_\_threadfence\_block: ensures that all writes (or reads) to the memory made by the calling

thread before the call to \_\_threadfence\_block are observed by all threads in the same ThB as

occurring before all writes (or reads) to the memory made by the calling thread after the call

to \_\_threadfence\_block.

- 2. \_\_threadfence: acts as \_\_threadfence\_block for all threads in the ThB of the calling thread and also ensures that no writes to the device memory made by the calling thread after the call to \_\_threadfence are observed by any thread in the device as occurring before any write to the device memory made by the calling thread before the call to \_\_threadfence.

- 3. \_\_threadfence\_system: acts as \_\_threadfence\_block for all threads in the ThB of the calling thread and also ensures that all writes (or reads) to the device or host memory made by the calling thread before the call to \_\_threadfence\_system are observed by all threads in the device, host threads, and all threads in peer devices as occurring before all writes (or reads) to the device or host memory made by the calling thread after the call to \_\_threadfence\_system.

It is important to notice that memory fence functions only affect the order of memory operations

on a thread. Hence, they do not ensure that these memory operations are visible to other threads. The memory operations are visible only if the other threads truly observe the device memory and not cached versions of it [36], which can be ensured by using the *volatile* keyword.

#### 2.2 Memory Hierarchy

In order to provide parallel processing and scalability capabilities, CUDA threads may access data from multiple memory spaces, where each one has its own characteristics, such as size, latency and bandwidth. Those memory spaces are exposed to the programmer to store data in the most performance-optimal way. Therefore, the data accesses must be carefully managed, in order to efficiently use the complex GPU memory hierarchy and to achieve high performance.

#### 2.2.1 Host Memory

Although the host memory does not belong to the GPU, the host memory can be accessed by kernels: it is called *zero-copy* memory space. Zero-copy is a feature that was introduced in version 2.2 of the CUDA Toolkit. A kernel is not allowed to allocate or free zero-copy memory, but may use pointers to such zero-copy memory space passed in from the host program. By doing so, the GPU threads can directly access the host memory as long as it is mapped/pinned to a non-pageable memory. On integrated GPUs, where the host and the device memory are physically the same, mapped/pinned memory provides always gains in performance because it avoids superfluous copies. On discrete GPUs, mapped/pinned memory is advantageous only in certain cases, since data is not cached on the GPU. In this case, performance gain may be obtained if the data is going to be accessed only once and if the data accesses are coalesced.

#### 2.2.2 Global Memory

The global memory is an off-chip large memory space that is visible to all threads. Since the global memory is usually implemented by an external Dynamic Random-Access Memory (DRAM), its latency can be hundreds of processor clocks. The host holds the responsibility for managing the global memory (e.g. to allocate memory space), as well as for data transfers between the host memory and the device memory space. In this global memory, it is possible to share data between threads of different kernels.

Although the order of memory reads and writes to the same address is preserved within a thread, the order of accesses to different addresses may not be preserved. In fact, accesses to the same global memory address by different threads are not guaranteed to have sequential consistency, since the ThB execution order is unknown. Nevertheless, *Memory Fence Functions* can be used to coordinate the global memory accesses. Moreover, atomic functions are available to guarantee memory accesses without interference from other threads.

#### 2.2.3 Constant Memory

The constant memory is a read-only memory space that is also accessible by all threads. Only the host can manage and store values in the constant memory space. Hence, just like the global memory, the constant memory is persistent across kernel launches by the same application. From the device perspective, the constant memory is immutable and may not be modified. In this way, the host must set the constant memory variables prior to launching a kernel.

#### 2.2.4 Texture Memory

The texture memory is a read-only memory space larger than the constant memory and it is also visible by all threads. This memory is meant to store immutable arrays. As the constant memory, only the host can manage and store values in the texture memory. However, contrasting to the global and constant memory spaces, texture memory offers different addressing modes, as well as data filtering for some specific data formats [36]. Texture fetches are cached in the processor cache hierarchy designed to optimize the throughput of texture fetches from thousands of concurrent threads. Since the texture memory (and the associated cache) was designed to be used with 3D graphics, by conveniently storing 2D arrays, they can be efficiently used as a better cache of the global memory for specific non-aligned memory accesses.

#### 2.2.5 Local Memory

The local memory is a private memory space that is visible only to a single thread. The local memory space resides in the device memory (off-chip), so local memory accesses have the same high latency and low bandwidth as global memory accesses. The local memory is architecturally larger than the thread's register file. Nevertheless, the compiler is likely to place several variables in the local memory, such as: *i*) arrays for which it cannot determine that they are indexed with constant values; *ii*) large structures or arrays that would consume too much register space; and *iii*) any variable, whenever the kernel uses more registers than available (this is also known as *register spilling*) [36].

#### 2.2.6 Shared Memory

The shared memory is an on-chip memory (much like an L1 cache) with low access latency and high bandwidth, which is visible to all threads in the same ThB. In this way, the shared memory traffic does not need to compete with limited off-chip bandwidth (e.g. for accessing global memory). Hence, it is practical to accommodate very high bandwidth memory structures on-chip to support the read/write demands. Moreover, variables and data structures stored in the shared memory exist from the time a ThB is created to the time it terminates.

The memory accesses in this memory space are also not ordered. Therefore, just like the global memory, atomic functions are also permitted in the shared memory. Moreover, synchronization points and memory fences can also guarantee the correct memory access order and coordinate the accesses between threads in the same ThB.

#### 2.3 Computational Architecture

For the sake of simplicity, only the NVIDIA GPU architecture details are going to be presented. Similar characteristics may be found on GPUs from other vendors. The NVIDIA GPU architectures are mainly composed of a scalable array of multithreaded Streaming Multiprocessors (SMs) [36]. When a kernel is issued by one stream, the ThBs of the grid are enumerated and distributed to the available SMs and with execution capacity. According to the SM capability, multiple ThBs can be concurrently executed on one SM and all the threads in a ThB are executed in only one SM. As soon as the ThBs finish their execution, new blocks are launched on the vacated SMs.

Since the SMs are designed to be highly multithreaded [42], it is possible to: *i*) hide the latency of memory accesses; *ii*) support fine-grained parallel graphics shader and computing programming models; *iii*) virtualize the physical processors as threads and ThBs to provide transparent scalability; and *iv*) simplify the parallel programming model, by preparing a serial program (kernel) for one thread. Hence, to manage and efficiently execute such a large amount of threads, the SM employs an architecture model designed as Single Instruction Multiple Thread (SIMT).

With SIMT, the SM is responsible for creating, managing, scheduling, and executing threads in groups of 32 parallel threads called *warps*<sup>2</sup>. Individual threads composing a warp start together at the same program address, but they have their own instruction address counter and register state and therefore can branch and execute independently [36]. Whenever a ThB is assigned to be run in a SM, the threads are split into warps and each warp gets scheduled by a warp scheduler of the SM for execution. Since a warp executes one common instruction at a time, the number of threads in a ThB should be multiple of 32, in order to avoid inactive device threads.

Moreover, full efficiency can only be achieved when all 32 threads of a warp agree on a common execution path. As soon as one thread in a warp diverges due to a conditional branch, the warp executes serially each execution path, by disabling all the threads that do not belong to that path. When all execution paths are completed, the threads shall converge back to the same execution path. Nevertheless, since different warps execute independently regardless of whether they are following common or disjoint execution paths, branch divergence degrades the performance only when it occurs with threads within a warp.

In terms of performance optimization, three main strategies should be taken into account in the

<sup>&</sup>lt;sup>2</sup>In the OpenCL framework, the warp concept is defined as *wavefront*. In AMD GPUs, for example, some of the low-end and older GPUs, such as the AMD Radeon HD 54XX series graphics cards, have a *wavefront* size of 32 threads. Higher-end and newer AMD GPUs have a *wavefront* size of 64 parallel threads. [43]

development of the kernels, according to the SM architecture:

- Maximize the degree of parallelism: each kernel should be implemented in such a way that

it exposes as much data parallelism as possible, allowing a large number of simultaneously

active threads.

- 2. **Instruction Throughput**: divergence control flow instructions in the threads of a warp (warp divergence) should be avoided in order to achieve maximum instruction throughput.

- 3. Memory Optimizations: data accesses of each module should be carefully managed, in order to efficiently take advantage of the complex GPU memory hierarchy, i.e., global, cache, shared, register, constant and texture memories. Moreover, memory access latency, coalesced accesses, bank conflicts, register spilling and memory bandwidth utilization should also be taken into account.

In fact, it should be taken into account that the amount of registers and shared memory available in the SM is limited. Hence, depending on the amount of registers and shared memory requested by the kernel, the number of ThBs and warps which can reside in a SM should be defined. If there are not enough registers or shared memory available per SM to process at least one ThB, the kernel will not be executed. These limits, as well the amount of registers and shared memory available on the SM, depend on the capability of the device.

Modern NVIDIA GPU architectures are also defined by their *compute capability*. The compute capability of a device is represented by a version number, sometimes also called its "SM version". This version number identifies the set of features supported by the GPU hardware and it is used by applications (at runtime) to determine which hardware features and/or instructions are available on the present GPU.

The compute capability comprises a major revision number X and a minor revision number Y and it is denoted by X.Y. Devices with the same major revision number have the same core architecture. The major revision number is 5 for devices based on the *Maxwell* architecture, 3 for devices based on the *Kepler* architecture, 2 for devices based on the *Fermi* architecture, and 1 for devices based on the *Tesla* architecture. The minor revision number corresponds to incremental improvements to the core architecture, possibly including new features.

Table 2.1 presents several technical details of NVIDIA GPUs. For example, *warp shuffle functions* are only available for compute capability 3.0 or higher. These functions, which were introduced by NVIDIA Kepler architecture, allow to directly share data between threads of the same warp without employing the shared memory. Hence, threads of a warp can read each others' registers by using a new instruction called *shuffle*. This functionality is not currently available in the OpenCL framework.

The *Throughput of 32-bit floating-point operations* presented in Table 2.1 represents the number of operations that can be executed per clock cycle per SM. This is related with the number of

| Technical Specifications                        |   | Compute Capability  1.0   1.2   2.0   3.0   3.5   5.0   5.2 |      |           |               |  |

|-------------------------------------------------|---|-------------------------------------------------------------|------|-----------|---------------|--|

| Warp shuffle functions                          |   | No I                                                        |      | Yes       |               |  |

| Throughput of 32-bit floating-point operations* | 8 |                                                             | 32   | 192   128 |               |  |

| CUDA cores for arithmetic operations per SM     |   | 8                                                           | 32   | 192 128   |               |  |

| Number of warp schedulers per SM                |   | 1                                                           | 2    |           | 4             |  |

| Maximum number of threads per ThB               |   | 1024                                                        |      |           |               |  |

| Warp size (in threads)                          |   | 32                                                          |      |           |               |  |

| Maximum number of resident ThBs per SM          |   | 8                                                           |      | 16        | 32            |  |

| Maximum number of resident warps per SM         |   | 32                                                          | 48   | 64        |               |  |

| Maximum number of resident threads per SM       |   | 1024                                                        | 1536 | 2048      |               |  |

| Number of 32-bit registers per SM               |   | 16 K                                                        | 32 K |           | 64 K          |  |

| Maximum amount of shared memory per SM          |   | 16 KB                                                       |      | i8 KB     | 64 KB   96 KB |  |

| Amount of local memory per thread               |   | 16 KB 512 KB                                                |      |           |               |  |

| Constant memory size                            |   | 64 KB                                                       |      |           |               |  |

| Number of shared memory banks                   |   | 32                                                          |      |           |               |  |

Table 2.1: GPU technical specifications, according to their Compute Capability.

cores per SM. Hence, the values in Table 2.1 should be multiplied by the number of existing SMs, in order to get the actual throughput for the whole device. For a warp size of 32, one instruction corresponds to 32 operations, so if N is the number of operations per clock cycle, the instruction throughput is N/32 instructions per clock cycle.

Table 2.1 also includes the maximum number of resident ThBs, warps and threads per SM, for the different compute capabilities. Similarly, the memory characteristics, such as the number of 32-bit registers per SM, the maximum amount of shared memory, the amount of local memory per thread and the constant memory size were also presented.

The shared memory is divided into equally-sized 32 memory modules, denoted as banks, which can be simultaneously accessed to achieve high bandwidth. Any memory request (read/write) made of x addresses that fall in x distinct memory banks can therefore be serviced in parallel, yielding an overall bandwidth that is x times as high as the bandwidth of a single module. However, if two addresses of a memory request fall in the same memory bank, there is a bank conflict, the accesses have to be serialized, thus decreasing the effective bandwidth. The hardware splits a memory request with bank conflicts into as many separate conflict-free requests as necessary, thus decreasing the throughput by a factor equal to the number of separate memory requests.

Table 2.2 presents a summary of the device memory features, which includes for each memory space: i) location (on/off chip); ii) whether it is cached; iii) how it is accessed, i.e., read/write (R/W); iv) visibility; and v) the lifetime of the memory space.

# 2.4 CUDA Alternatives for Extended Portability: OpenCL

The information that was provided for the NVIDIA programming model (i.e., CUDA), as well as the terminology associated to those GPU architectures is easily extended to other frameworks,

<sup>\*</sup>Add, multiply, multiply-add.

|              |          |        |        | -                  |          |

|--------------|----------|--------|--------|--------------------|----------|

| Memory Space | Location | Cached | Access | Visibility         | Lifetime |

| Register     | On chip  | n/a    | R/W    | 1 thread           | Thread   |

| Local        | Off chip | Yes*   | R/W    | 1 thread           | Thread   |

| Shared       | On chip  | n/a    | R/W    | All threads in ThB | ThB      |

| Global       | Off chip | **     | R/W    | All threads + host | Host     |

| Constant     | Off chip | Yes    | R      | All threads + host | Host     |

| Texture      | Off chip | Yes    | R      | All threads + host | Host     |

<sup>\*</sup>Cached in L1 and L2 by default on devices of compute capability 2.x and 3.x; devices of compute capability 5.x cache locals only in L2.

such as OpenCL. As stated before, both CUDA and OpenCL provide similar functionality, where the OpenCL framework allows code portability among different devices.

In order to allow such aimed portability among different devices and architectures, OpenCL code is compiled at runtime. Nevertheless, the programming model and the assumed memory hierarchy are similar to CUDA, which have been presented in Sections 2.1 and 2.2. Table 2.3 presents a comparison between the terminology used in CUDA and OpenCL. For example, thread, ThB, shared memory and local memory in CUDA are denoted as work-item, work-group, local memory and private memory in OpenCL, respectively.

Nevertheless, since OpenCL is a language capable of being executed across several different platforms (e.g. CPUs, GPUs, Digital Signal Processors (DSPs) and FPGAs among others), the capabilities made available to current massively parallel computational hardware (such as GPUs) are sometimes limited. As an example, in some NVIDIA GPUs, where the L1 cache and shared memory use the same hardware resources, it is possible to configure the amount of shared memory per SM per kernel by using CUDA. This feature allows to fine tune the kernels that could achieve higher performance (e.g., in kernels which do not require shared memory, could take advantage of a larger L1 cache). OpenCL does not support such architecture-specific settings.

Table 2.3: Comparison between the terminology used in CUDA and OpenCL.

|                    | <u> </u>           |

|--------------------|--------------------|

| CUDA Terminology   | OpenCL Terminology |

| Thread             | Work-item          |

| Thread Block (ThB) | Work-group         |

| Global Memory      | Global Memory      |

| Constant Memory    | Constant Memory    |

| Shared Memory      | Local Memory       |

| Local Memory       | Private Memory     |

|                    |                    |

<sup>\*\*</sup>Cached in L1 and L2 by default on devices of compute capability 2.x; cached only in L2 by default on devices of higher compute capabilities, though some allow opt-in to caching in L1 as well via compilation flags.

# 2.5 Summary

In this chapter, a brief overview about modern GPU architectures, namely their programming model and memory hierarchy, was presented. Moreover, the architectural features of NVIDIA GPUs have been briefly discussed in order to provide the required information for supporting the remaining chapters of this Thesis. In particular, the kernels designed in Chapter 4 for the GHEVC video decoder shall maximize the *parallelism degree*, *instruction throughput* and optimize *memory accesses* [44].

# 3

# **Background and State of the Art**

#### **Contents**

| 3.1 | General Overview of the HEVC Standard | 20 |

|-----|---------------------------------------|----|

| 3.2 | Complete HEVC Decoder Implementations | 36 |

| 3.3 | Summary                               | 39 |

In this chapter, the background on HEVC is provided, together with the state-of-the-art on HEVC decoder implementations.

#### 3.1 General Overview of the HEVC Standard

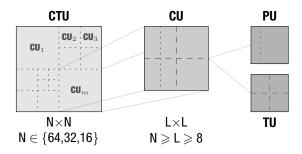

According to the HEVC standard, a video frame is decoded from the received bitstream in data element units corresponding to square pixel blocks. These pixel blocks are denoted as Coding Tree Units (CTUs) [45], whose size information  $(N \times N)$  is decoded from the received bitstream. Possible values for N are 64, 32 and 16 pixels [4]. Each CTU is further split into square blocks with  $L \times L$  pixels, named Coding Units (CUs), by following a quadtree structure [5]. The dimension of the CUs (L) varies between a maximum size of N pixels to a minimum size of 8 pixels, as shown in Figure 3.1.

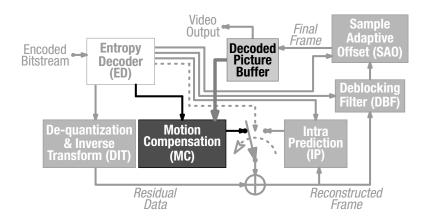

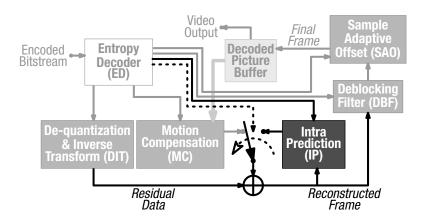

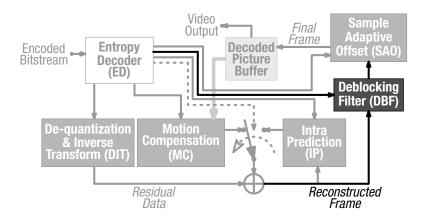

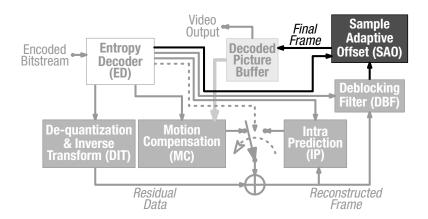

Each CU encloses a Prediction Unit (PU) and a Transform Unit (TU) [45], used for generating the prediction pixel block and the corresponding residual data, respectively. The prediction pixel block can be obtained either by using the data from the same frame (intra prediction) or from previously decoded frames (inter prediction). A general framework of an HEVC decoding structure, together with the corresponding module integration, is presented in Figure 3.2.

As defined by the standard, an HEVC decoder consists of the following main modules:

- **Entropy Decoder**: decodes the input bitstream and collects the required data to decompress the video sequence.

- **De-quantization and Inverse Transform (DIT)**: recovers the pixel residues by dequantizing the entropy decoded coefficients and by applying the inverse integer transforms to such coefficients, reverting them into the pixel domain, by considering up to four different block sizes and five integer discrete transforms [46].

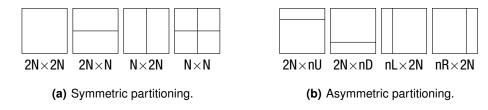

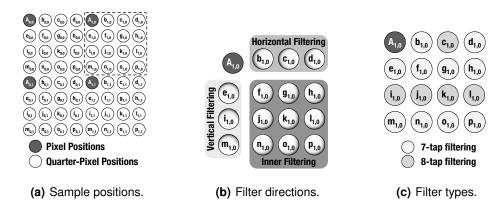

- Motion Compensation (MC): reverts the PU inter prediction, by considering the previously

decoded frames as reference frames, as well as symmetric and asymmetric partitions,

quarter-pel motion vectors, multiple reference frames and an interpolation procedure with up

to 8-tap filters [47].

Figure 3.1: Example of the CTU partitioning into CUs, PUs and TUs.

Figure 3.2: Block diagram of an HEVC decoder.

- Intra Prediction (IP): executes the PU intra prediction, where the spatial prediction mechanism considers only the already reconstructed neighboring pixels of the current frame to predict the current block, which is subsequently added with the residual data computed by the DIT [48]. Several block sizes have to be considered, as well as thirty five different IP modes that are specified by the HEVC standard [48]. Since each prediction mode takes into account the reconstructed pixel samples of the neighboring blocks, it must respect strict data dependencies imposed by the HEVC standard. These dependencies do not only occur between adjacent data blocks within the IP module, but also across the DIT and IP modules;

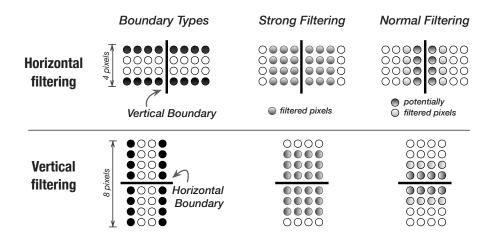

- **Deblocking Filter (DBF)**: reduces the blocking artifacts of the reconstructed blocks from the hybrid video coding<sup>1</sup>. The DBF is applied to a 8×8 sample grid of the frame, where the vertical edges are processed first, followed by the horizontal ones [50].

- Sample Adaptive Offset (SAO): improves the overall image quality, by reducing the CTU sample distortion according to a set of parameters selected at the encoder [51].

The decoding procedure, depicted in Figure 3.2, starts by decoding the *Encoded Bitstream*, using the *Entropy Decoder* module, in order to obtain the coefficients, as well as all other information required to decompress the video sequence. The coefficients are then de-quantized and inverse transformed by the DIT module, in order to obtain the residual data. Then, the reconstructed image blocks are obtained by adding the residual data from the DIT module to the predicted image blocks, computed either in the IP or in the MC modules. Then, DBF is applied to attenuate blocking artifacts introduced by the block-based prediction and transform coding. Finally, the mean sample distortion is reduced in the SAO module, where the final *Video output* is produced.

It is important to notice that the reconstruction process (DIT, MC and IP) is executed at block-level, where the CTUs are processed in raster-scan order. Inside each CTU, the CUs are decoded

<sup>&</sup>lt;sup>1</sup>The hybrid video coding scheme combines temporal prediction between pictures of the video sequence with transform coding techniques for the prediction error [49].

by following a z-scan order, as well as the PUs and the TUs within each CU. On the other hand, the in-loop filters (DBF and SAO) are applied at frame-level on the reconstructed frame.

Although most of the HEVC procedures provide a high level of parallelism, the bottlenecks (in terms of parallelization) are the IP and the *Entropy Decoder*, as presented in [24].

#### 3.1.1 Entropy Decoder

As defined by the HEVC standard, a video bitstream is a set of encoded syntax elements, which carry the information on how the video signal can be reconstructed at the decoder [52] (see Figure 3.3). These syntax elements are encoded with three coding schemes: fixed length codes, zero-order Exponential-Golomb code and arithmetic coding [53]. As a consequence of the rather efficient encoding success of the H.264/MPEG-4 AVC Context-Adaptive Binary Arithmetic Coding (CABAC) [54], a similar but still improved coding scheme was adopted in the HEVC standard, which improves the throughput, memory requirements and compression performance [55].

The CABAC coding engine requires the transformation of non-binary syntax elements into a binary representation before encoding. This process is called *binarization*, where each binary symbol is named as *bin*. Each *bin* is then coded according to its respective *probability model* (or *context model*), where the probabilities for the two possible binary values "0" and "1" are stored. The *context model* can be static, with uniform probability distribution, or adaptive, when the probability distribution is updated at each coded symbol. At the decoder side, the encoding process is reversed to reveal the coded syntax elements from the bitstream. Hence, the CABAC context adaptability guarantees high coding efficiency but also increases the data dependency and unpredictability of the *Entropy Decoder* module, which restricts parallel implementations.

Therefore, in order to increase the level of parallelism of the *Entropy Decoder* module, the CABAC data dependencies are reduced in the HEVC standard by three frame-level parallelization strategies: slices, tiles and Wavefront Parallel Processing (WPP) [56]. Each picture of the video

Figure 3.3: Block diagram of an HEVC decoder: entropy decoder.

sequence is divided into one or more slices, where slices are regions of the frame composed of an integer number of CTUs that can be independently decoded. However, although the entropy decoding and the reconstruction frame process of a slice may be performed independently from other slices of the frame, there are still potential dependencies regarding the cross-slice border in-loop filtering. There are three types of slices:

- I Slice: all PUs are intra predicted.

- P Slice: each PU may be intra or inter predicted, where the motion compensation is performed on a single reference frame from the reference picture list with a single PU motion vector.

- **B Slice**: each PU may be intra or inter predicted, where the motion compensation is performed with up to two reference frames from two reference picture lists.

Nevertheless, the coding efficiency usually decreases when the number of slices per frame increases, mainly due to the slice header overheads and reduced spatial redundancy exploitation.

On the other hand, a tile is a new video coding parallelization strategy defined by the HEVC standard. A tile is a rectangular region of the frame that can be independently decoded from the other tiles of the frame [57], but which provides more parallelism to be exploited by parallel architectures. However, although the entropy decoding and the reconstruction frame processing of a tile are performed independently from other tiles of the frame, the in-loop filtering can still be applied over tile boundaries to avoid tile border artifacts. Moreover, if multiple slices are employed with tiles, one of the following conditions shall be true per slice and per tile: *i*) all CTUs of a slice belong to the same tile or *ii*) all CTUs of a tile belong to the same slice. Hence, although the tile coding efficiency is higher than when multiple slices are used, it decreases when the number of tiles increases, which limits the parallelization efficiency [56].

Just like the tile strategy, the WPP has been introduced by the HEVC standard to take advantage of multi-threading architectures. Each CTU row of the frame can be decoded with a different thread. Nonetheless, to exploit statistical redundancy, each CTU of a frame can only be processed if the two consecutive and immediately above CTUs have been already decoded, which provides a wavefront approach. Although the WPP parallelism level is limited by the frame size, a new strategy based on WPP, called Overlapped Wavefront (OWF), has been introduced in [56], which improves the efficiency of the WPP, by overlapping the execution of consecutive frames.

#### 3.1.2 De-quantization and Inverse Transform

Figure 3.4 highlights DIT procedure in the HEVC block diagram. This module is responsible for recovering the *Residual Data* from the entropy decoded coefficients. As referred before, the TUs in each CU are split into smaller blocks  $(4\times4, 8\times8, 16\times16 \text{ or } 32\times32)$  according to a quadtree structure [58]. These blocks are named as Transform Blocks (TBs), and each TU is

Figure 3.4: Block diagram of an HEVC decoder: de-quantization and inverse transform.

composed by one luma and two chroma TBs. Similarly to H.264/MPEG-4 AVC, only integer core transforms are specified by the HEVC standard, in order to avoid the introduction of rounding drifts, both at the encoder and the decoder, caused by rounding on floating point computation. As a consequence, the HEVC  $4\times4$  to  $32\times32$  transform operations are based on the integer Discrete Cosine Transform (DCT) [46]. The inverse DCT kernels are the same for luma and chroma TBs, except for the  $4\times4$  luma TB of intra blocks, for which an integer inverse Discrete Sine Transform (DST) is applied.

The DIT procedure (see Figure 3.5) is directly applied on the *TB coefficients* obtained from the entropy decoder, in order to obtain the *TB Residual Data*. A more in-dept discussion about the details of transform coefficient coding [59] (such as coding methods for the last significant coefficient, significance map, coefficient levels and sign data) are beyond the scope of this thesis.

#### 3.1.2.A Residual Data Decompressing

For each TB, the overall procedure is controlled by three flags [60]:

- Transquant Bypass Flag (TBF): to indicate a bypass operation over the inverse transform

and de-quantization procedures. This flag is encoded at CU-level, at the beginning of the

CU syntax structure. Moreover, this flag enables a perfect reconstruction for a lossless

representation of the coded block, since the residual signal is directly coded without any

degradation [61, 62].

- Coded Block Flag (CBF): indicates the presence of nonzero transform coefficients at the TB-level. If this flag is unset, the corresponding TB Residual Data is a null block.

- Transform Skip Flag (TSF): to indicate a skipping of the inverse transform at the TB-level. Usually, this technique improves the compression efficiency of screen-content video sequences, which contains text and graphics [60].

Figure 3.5: The HEVC residual data decompressing flowchart.

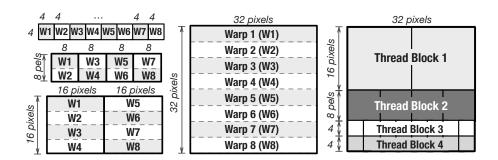

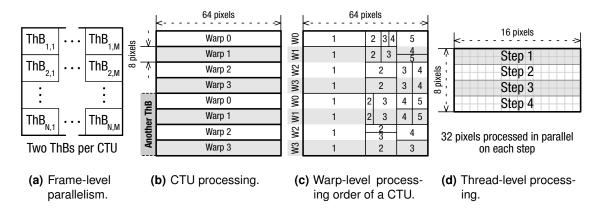

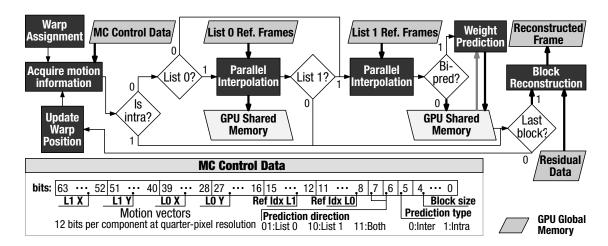

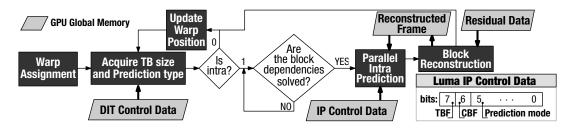

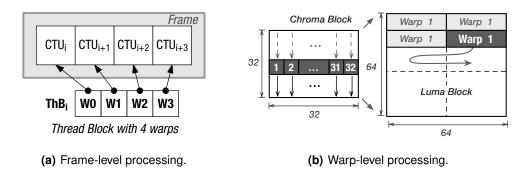

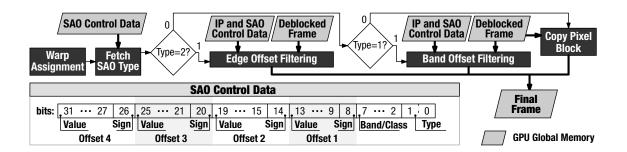

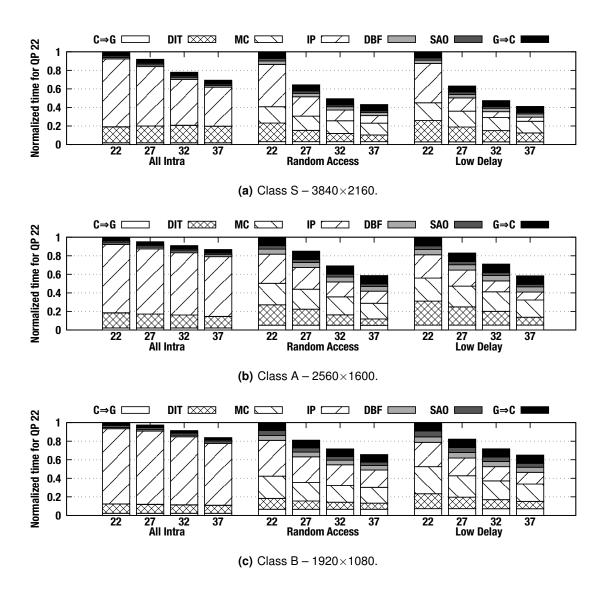

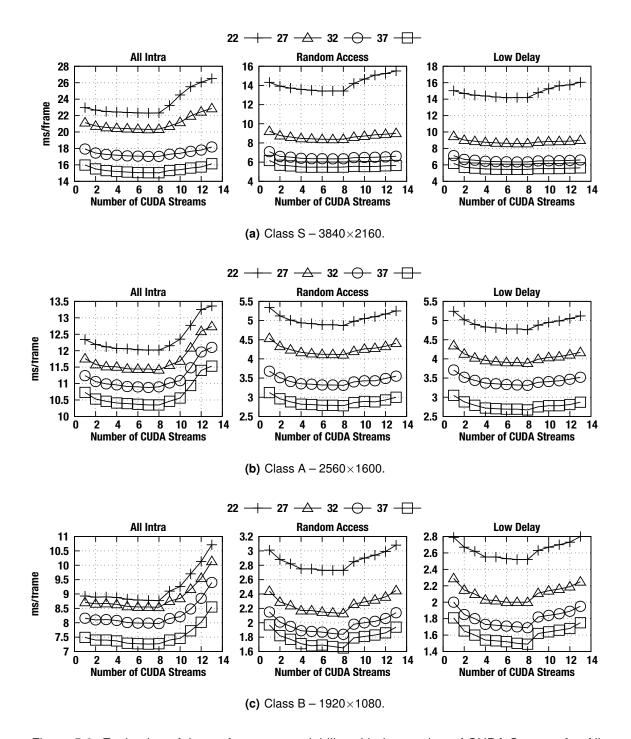

The overall procedure of the DIT module is presented in Figure 3.5. Whenever the TBF is set, DIT is bypassed, which means that the residual data directly corresponds to the TB coefficients. To achieve lossless CTU (or frame) reconstruction, the TBF can be used by the encoder to bypass not only the DIT module, but also the DBF and the SAO modules. If the TBF is unset and the CBF is set, the de-quantization procedure must be applied to the TB coefficients. The *De-quantization* module also implements the HEVC inverse scaling, which depends on the Quantization Parameter (QP) and on the adopted TB size [4]. Finally, the TSF signals the decoder to skip the inverse transform and to apply only the *TSF Scaling* (TSF=1). When TSF is not set, the *2D Inverse Transform* is performed on the de-quantized data block, by computing two 1D decompositions (i.e., *1D Column* and *1D Row Inverse Transforms*). Each decomposition is followed by a specific scaling procedure to perform the normalization in the transform domain [46]. Each 1D decomposition is performed on a specific *transform coefficient array*, which is chosen with respect to the adopted TB size and prediction mode.